《1、 引言》

1、 引言

传统天线通常是根据给定系统的规范设计的,包括波束方向图、天线增益、旁瓣电平(SLL)和极化。为了满足各种先进通信系统和多功能平台的需求,近年来可重构天线技术得到了越来越多的关注并迅速发展[1‒2]。通过采用开关、调谐设备和先进材料等,可重构天线可实现实时地改变天线特性以满足系统要求。可重构天线可分为方向图可重构天线、频率可重构天线和极化可重构天线[3‒5]。迄今为止,大多数公开报道的可重构天线是单元天线的形式。

对于接收系统而言,采用具有多极化功能的可重构天线可以有效减少极化失配损失。在参考文献[6‒15]中介绍了许多具有两个正交圆极化(CP)和两个正交线极化(LP)可重构能力的天线。然而,当这些天线用于接收任意LP信号时,它们仍可能遭受高达50%的极化失配损失。因此,为了提高接收任意LP波时的信号质量,在参考文献[16‒25]中,研究人员提出了各种多线极化可重构(MLPR)天线。一般来说,MLPR天线可以细分为两类:辐射器可重构天线[16‒20]和馈电网络可重构天线[21‒25]。通过将射频(RF)开关,比如正极-本征层-负极(PIN)二极管,加载到可重构结构中,就可以通过配置开关的通断状态来控制天线的极化。

在大多数实际系统中,通常需要较高的天线增益和一定程度的波束控制,因此常使用天线阵列。据了解,只有少数文章报道了关于多极化天线阵列的研究[26‒32]。在文献[26]中,作者提出了一种具有可旋转天线单元和移相器的阵列,该阵列可以改变辐射波的极化椭圆率。在参考文献中[27]中,作者设计了一个均匀排布的交叉偶极子天线阵列,用于接收两个正交分量的射频信号。该天线阵列可用于估计入射波的到达方向和极化。然而,参考文献[26‒27]中报道的技术均需要复杂的幅度和相位控制网络。此外,这些天线阵列只是从理论上进行设计的,并没有经过实际阵列的验证。在参考文献[28]中,作者设计了两个具有三个单元的极化捷变有源微带贴片天线阵列。该阵列采用的单元天线通过加载晶体管,实现了圆极化状态和LP状态。然而,该阵列的交叉极化电平(XPL)常常高于-12 dB。在参考文献[31]中,作者报道了一个1 × 4的可重构孔径馈电的贴片天线阵列。通过在交叉孔径上加载可控的射频开关,该阵列可实现± 45° LP可重构。然而,该阵列的XPL为-10 dB。此外,SLL是天线阵列的重要品质因数。降低阵列方向图的SLL可以增强天线阵列的抗干扰能力。许多文章已报道了采取各种方法来优化阵列单元的幅度、相位和位置以降低阵列SLL的研究[33‒36]。例如,遗传算法(GA)[33]、粒子群优化(PSO)[34]、快速傅里叶变换(FFT)[35]以及凸优化(CVX)技术[36]。然而,这些研究提出的阵列通常需要采用不等分的功率分配器馈电,增加了阵列设计的复杂性和难度。之后,在参考文献[37]中,作者提出了通过优化阵列中偶极子天线单元的朝向,可以在约束XPL的情况下降低SLL。使用这种技术,可以在不使用不等分功率分配器的情况下降低阵列的SLL。在参考文献[38]中,该技术得到进一步发展,作者通过从一组离散角度中适当地选择单元朝向成功地降低了SLL。在参考文献[39‒41]中,单元天线的极化方向被开发成为阵列波束控制的优化变量。然而,这些研究仅关注通过单极化天线单元的旋转来形成某个固定极化下的波束。上述研究提出的阵列缺乏在实现极化可重构功能的同时降低SLL的能力。

本文提出了一种采用多线极化单元的极化可编程阵列天线的新概念。该阵列由许多具有有限极化状态数量的极化可重构天线单元组成。通过采用一种新的优化策略并对所有阵列单元的极化状态进行编程,证明了该阵列可以在矢量辐射方向图中实现任何期望的LP,并精确控制SLL和XPL,从而完美地实现期望的极化以匹配通信信号,且该阵列仅需采用等分功率分配器馈电。为了验证所提出的概念,本研究设计并加工了一个由16个天线单元组成的阵列原型,其每个天线单元可实现8种极化状态。该可重构阵列由现场可编程逻辑门阵列(FPGA)控制以实现实时操作。对于不同的期望LP,该阵列实现了低于-16 dB的SLL和XPL,验证了所提出的技术和方法。该阵列在不同状态下共同覆盖的阻抗带宽为8.6%,覆盖4.77~5.20 GHz,阵列在优化的极化状态配置下的最大增益为17.34~17.53 dBi。据了解,这种阵列天线是首次被报道。

《2、 阵列天线系统模型和优化策略》

2、 阵列天线系统模型和优化策略

在本节中,首先介绍提出的阵列天线模型,然后阐述极化状态优化策略。后者包括优化单元极化状态和使用二进制遗传算法(BGA)在任何期望的LP下来实现具有期望的SLL和XPL的方向图。

《2.1 多线极化可重构天线阵列》

2.1 多线极化可重构天线阵列

考虑一个由N个MLPR天线单元组成的线性阵列,每一个单元天线可独立地在M个极化状态之间切换,如图1所示。那么这个阵列总共有M个可能的极化状态。天线单元沿x轴均匀排列,单元间距为d。阵列单元由等幅度的功率分配器馈电,每个天线单元的极化状态都由FPGA控制。对于阵列中的第n单元,用一个二进制数P,来表示其第m个极化状态的通断情况。若P,= 1,则表示第n单元的第m个极化状态被导通,P,= 0则表示该状态被关闭。显然,当第n单元的第m个极化状态被导通时,该单元的所有其他极化状态都将被关闭。换句话说,每个单元有且仅有一个极化状态被导通。因此,该阵列的方向图在考虑互耦效应下可以被描述为:

(1)

式中,

(2)

式中,

《图1》

图1 极化可编程阵列天线模型示意图。θ:以z轴正方向为基准的俯仰角;ϕ:以x轴正方向为基准的方位角;d:单元间距。

已知第n单元的VAEP可由单位向量和分解:

(3)

这样,可以得到:

(4)

对于该MLPR天线阵列,希望它能够在任意期望的LP d上产生辐射,同时控制SLL和XPL。然而,一个问题是d通常是一个固定的表示方向的单位向量,由

(5)

《图2》

图2 测量天线CoP方向图的示意图。

于是,实际实现或测量的CoP方向图如下:

(6)

在测试交叉极化(XP)方向图时,探头天线在θ = 0°处的极化与d正交。然后,可通过如下公式获得XP方向图:

(7)

在参考文献[42]中已提出上述关于CoP和XP的定义,该定义被称为Ludwig关于极化的第三定义。有了这个定义,一旦得到了阵列矢量方向图的和分量,就可以计算出在期望极化为d时的阵列CoP和XP方向图。

本文的主要关注点在于通过优化阵列的极化状态配置

为了在任意期望LP上产生降低SLL的辐射,可以优化阵列极化状态配置

(8)

式中

(9)

式中,W1和W2是用户定义的加权因子。这里的θ是副瓣区域的采样角度,其中a = 1, 2,

为了能够计算含耦合的阵列辐射方向图,需要获得每个单元的VAEP。理论上,VAEP可以通过全波电磁仿真获得。然而,由于相互耦合效应,单元天线的VAEP不仅与其自身的极化状态有关,而且在阵列环境中还会受到其相邻单元极化状态的影响。因此,为了能够使用极化状态选择的方法来获得所需的阵列方向图,需要获取每个单元在各种阵列极化状态配置下的各个极化状态的VAEP。那么总共需要获取M个耦合单元方向图。比如说,如果阵列有16个单元,并且每个单元有8个极化状态(即N = 16和M = 8),则总共需要获取816个VAEP。这是不符合实际情况的。因此,为了能够优化MLPR天线阵列的单元极化状态,必须采取一个良好的近似方法来获得不同极化状态配置下的单元天线的VAEP。

《2.2 MLPR天线阵列的方向图近似方法》

2.2 MLPR天线阵列的方向图近似方法

为了获得阵列单元的VAEP用于优化,假设由于单元极化状态的变化引起的相互耦合变化对VAEP的影响不大。如果在阵列极化状态优化的过程中单元极化状态变化很小,那么这个假设通常是成立的。于是,单元的方向图主要受其自身极化状态变化的影响。在这种情况下,如果选择的MLPR天线单元是旋转对称结构,则天线单元从一个极化状态切换到另一个极化状态可被视作天线的旋转。于是,可以数学地旋转在某个极化状态下获得的单元的VAEP来获取该单元在其他极化状态下的VAEP。假设阵列极化状态配置为

(10)

式中

(11)

于是,通过将方程(11)代入方程(4),工作在

(12)

根据方程(6)和方程(7),阵列在

(13)

通过对

《2.3 极化状态精炼优化策略》

2.3 极化状态精炼优化策略

由于采用的阵列单元的VAEP是通过方程(10)和方程(11)描述的近似方法获得的,因此方程(13)描述的阵列CoP和XP方向图会存在近似误差。一般来说,方程(12)和方程(13)中的阵列方向图的准确性取决于

在该策略的初始步骤中,所有N个单元的极化状态都设置为满足最小化

第n单元的可选极化状态范围可以描述为

(14)

在下面图表中给出的算法中详细介绍了提出的MLPR天线阵列的极化状态精炼优化策略的整个流程。在这个策略中,离散的极化状态优化问题可以看成是一个非线性整数规划问题。一般来说,随机优化算法,如BGA [33]、二进制PSO(BPSO)[34]和二进制差分演进(BDE)[43]适合用于解决这个问题,因为它们能够找到全局最优解。在本文中,采用BGA作为优化算法,详细过程整理在了下面的子程序中。BGA是一种相对有效和实用的优化方法,且已被用于解决阵列天线领域的许多优化问题[33]。利用BGA的优化机制,阵列极化状态配置将在适应度函数方程(8)的引导下迭代地得到优化。

在实际应用中,可以针对用户期望的LP优化阵列极化状态配置并将它们存储起来;然后,通过FPGA等控制设备,就可以实现阵列极化的编程控制。这样,通过使用FPGA控制阵列极化状态配置,阵列就可以产生任何期望LP上的辐射,同时约束其方向图的SLL和XPL。

《3、 极化可编程阵列天线的设计》

3、 极化可编程阵列天线的设计

在本节中,设计了一款具有8个LP状态的MLPR贴片天线,并将该天线用于构建16元极化可重编程阵列天线。然后,为了实现不同极化下的方向图,通过本文提出的策略优化天线阵列的极化状态配置,从而验证极化可编程阵列天线的概念。

《3.1 MLPR单元天线设计及其仿真性能》

3.1 MLPR单元天线设计及其仿真性能

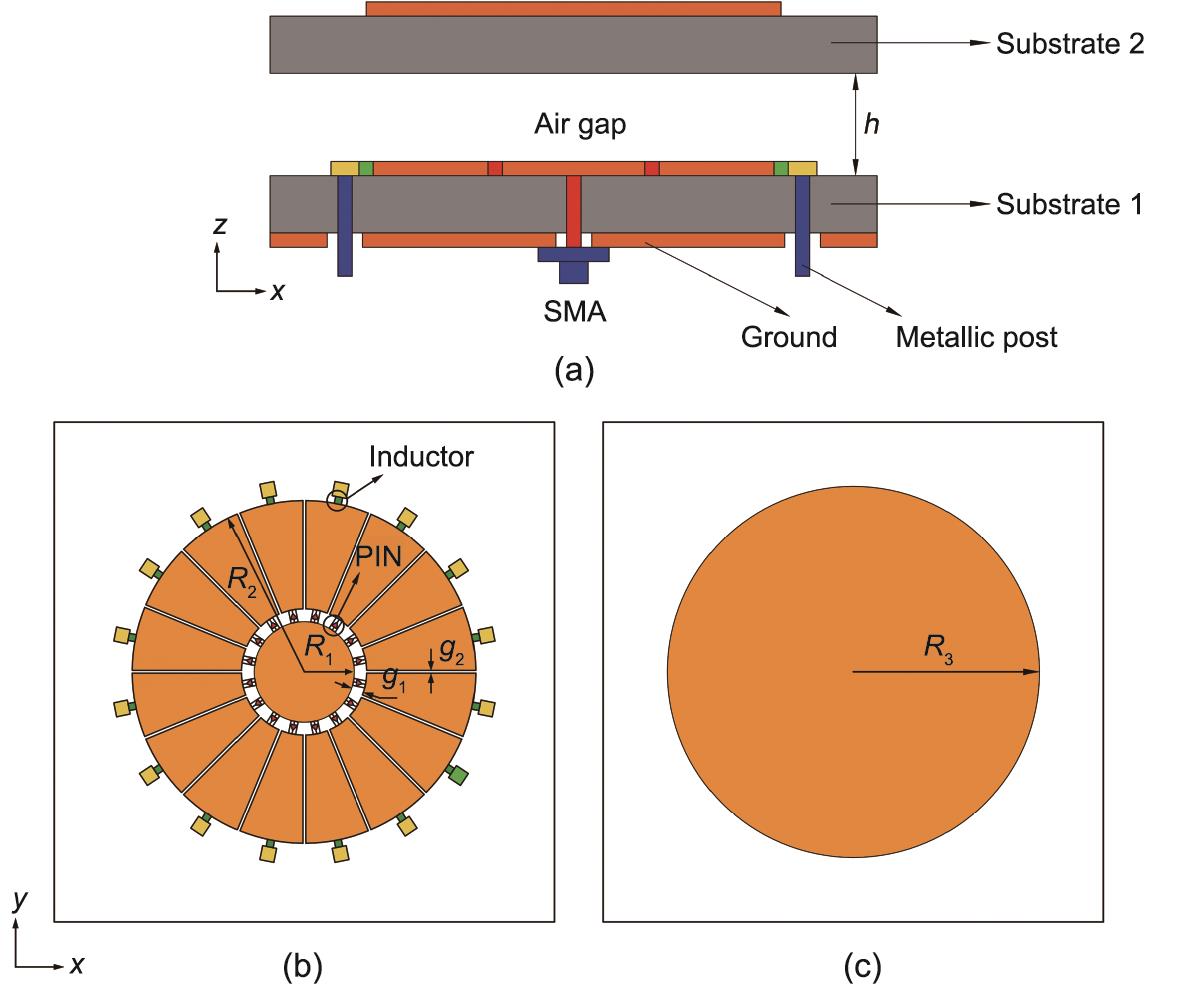

开发了一款8-LP可重构天线作为阵列单元。该单元基于环形槽贴片结构,可实现以22.5°为间隔的360°极化扫描[23]。如图3(a)所示,该天线单元由两层介质板组成,它们之间有3.7 mm的空气间隙。介质板1和介质板2均使用介电常数(εr)为4.4、损耗角正切(tanδ)为0.009的玻璃纤维环氧树脂覆铜层压板(FR-4)。介质板1和介质板2的厚度分别为0.6 mm和0.3 mm。天线的可重构辐射体印刷在介质板1的顶层,如图3(b)所示。该天线的可重构辐射体是一个被环形槽分割成两部分的圆形贴片。环形槽外边的辐射体部分又被16个间隙均匀地分成16块,用以实现极化可重构。PIN二极管焊接在这16个贴片和环形槽内的圆形贴片之间,用作极化可重构的开关。在可重构辐射体外边均匀地印刷了16个焊盘,用于连接直流(DC)偏置。电感器桥接在这些直流焊盘和可重构辐射体之间,它们可以在导通直流的同时阻断射频信号。天线的接地平面印在了介质板1的底层。在介质板2的顶层有一个圆形贴片,如图3(c)所示。该圆形贴片是天线的寄生贴片,用以提高天线性能。该单元天线由50 Ω同轴电缆馈电,如图3(a)所示。同轴电缆的内导体和外导体分别连接到介质板1顶部的内圆形贴片和介质板1底部的接地平面。一些金属柱垂直地穿过介质板1,连接到其顶层的焊盘上,用作直流偏置线。在图3的图题中给出了该天线详细的尺寸参数。

《图3》

图3 提出的8-LP可重构天线的几何结构图。(a)沿x轴的剖面视图;(b)介质板1的俯视图;(c)介质板2的俯视图。天线尺寸为:内圆形贴片半径(R1)为3.6 mm,辐射体贴片半径(R2)为8.65 mm,寄生贴片半径(R3)为10.5 mm,环形槽宽度(g1)为0.5 mm,分隔间隙宽度(g2)为0.2 mm,空气间隙高度(h)为3.7 mm。SMA:超小型A型号。

这里采用的PIN二极管是Infineon公司生产的0603封装的Bar50-02V。该二极管在导通状态下等效于一个3 Ω电阻与一个0.6 nH电感串联;而在断开状态下,它等效为一个5000 Ω电阻与一个0.1 pF电容并联再串联一个0.6 nH的电感(有关其性能的详细信息,感兴趣的读者可以阅读参考文献[44])。天线中采用的电感为0402封装的VHF100505HQ4N7ST,其电感值为4.7 nH,由广东风华高新科技股份有限公司生产。它可以有效地阻隔4.5~5.5 GHz的射频信号,同时导通直流[45]。本研究开发的天线处于工作状态时,需要有8个相邻的PIN二极管被同时导通。当PIN二极管导通时,其阴极通过内圆形贴片和同轴电缆的内导体连接到直流电源的负极,而二极管的阳极通过金属柱连接到直流电源的正极。如图4所示的天线工作状态示意图,其中红色的部分表示导通,蓝色的部分表示断开,这样,天线就工作在0°极化状态了。可见,将这样的PIN二极管通断配置按圆周方向旋转,该天线就能以22.5°为间隔产生8个不同的LP状态。

《图4》

图4 开发的MLPR天线的可实现的极化状态。其中红色的二极管导通,蓝色的二极管断开。在这种配置下,天线实现了0°极化状态

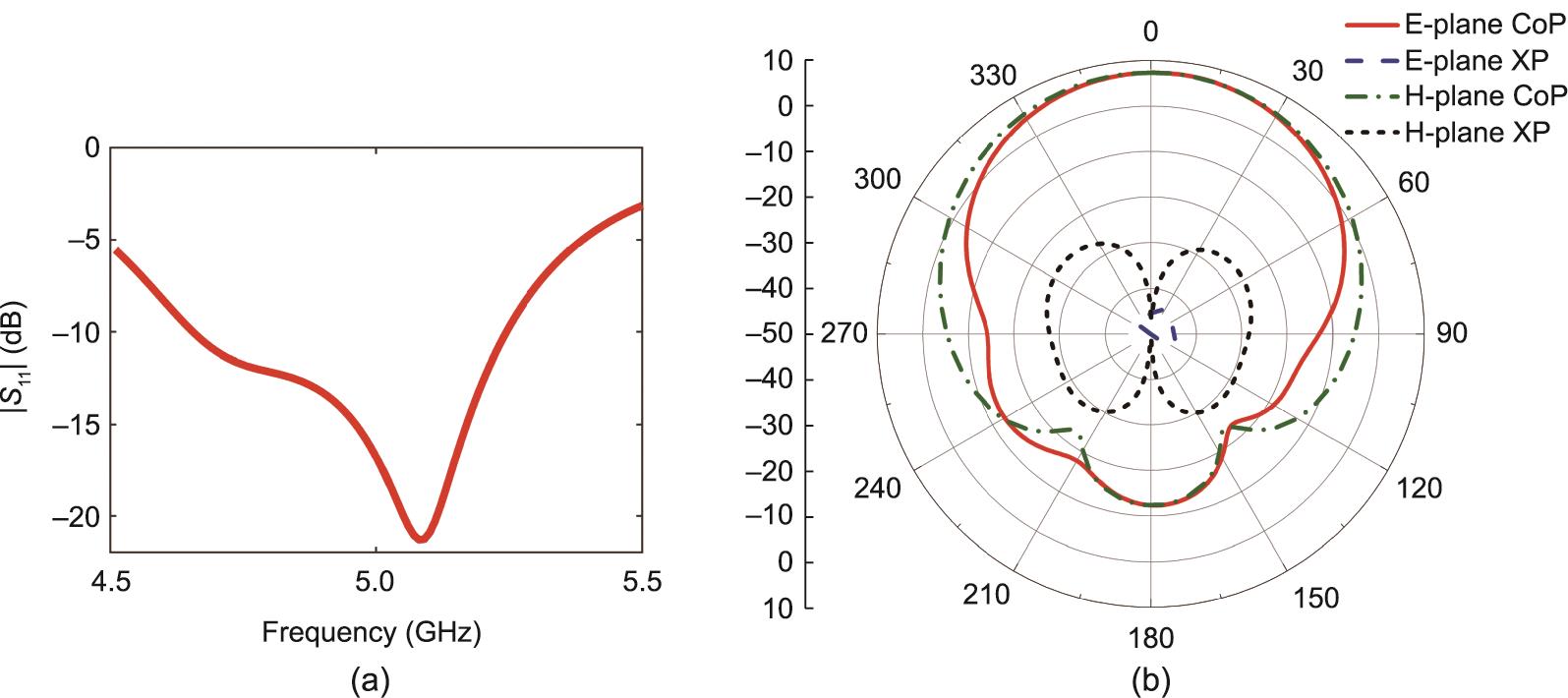

本研究采用高频结构仿真器(HFSS)仿真了开发的单元天线。由于该天线的结构具有旋转对称性,因此天线在不同极化状态下的性能几乎相同。为了简单起见,本文只展示天线工作在0°极化状态下的性能。由图5(a)可知,天线的仿真带宽为12.2%,覆盖了4.63~5.23 GHz [天线回波损耗(

《图5》

图5 开发的MLPR天线在0°极化状态下的仿真性能。(a)

《图6》

图6 加载两种不同的PIN二极管模型实现的MLPR天线单元的增益曲线(仿真)(a)和辐射效率(仿真)(b)。模型A:等效电路模型;模型B:理想模型。

《3.2 单元方向图近似方法的验证与分析》

3.2 单元方向图近似方法的验证与分析

采用上述MLPR单元天线构建了一个16单元均匀排布的线性MLPR天线阵列,单元间距为30 mm(5 GHz的半波长)。通常而言,不同单元之间的端口隔离度是阵列天线重要的性能指标之一。对于本文提出的MLPR天线阵列,不同的单元极化状态会影响端口隔离度。为了研究不同极化状态对端口隔离的影响,本研究检查了阵列的

《图7》

图7 当第8单元的极化状态从0°状态切换到90°状态时,天线阵列仿真的

另一方面,由于单元间互耦的存在,在阵列环境中的各个单元的方向图也会不同。并且,对于本文提出的MLPR天线阵列,单元方向图形状可能还会受到单元极化状态分布的影响。因此,当采用方程(10)中的方法,数学旋转单元在某一个极化状态下的方向图,以获取该单元在其他极化状态下的方向图时,可能会存在一些近似误差。为了分析方程(10)中这种近似方法的性能,把第8单元的极化状态从0°状态切换到[22.5°, 45.0°, 67.5°, 90.0°]状态,然后对比通过全波仿真获得的该单元的VAEP和通过方程(10)中的近似方法获得的结果。本文将第8单元在[0°, 22.5°, 45.0°, 67.5°, 90.0°]极化状态下的VAEP分别记作

《图8》

图8 将第8单元在0°状态下的VAEP数学旋转得到的近似VAEP与第8单元在不同极化状态下全波仿真得到的实际VAEP进行比较。(a)22.5°状态;(b)45°状态;(c)67.5°状态;(d)90°状态。观测面为xz平面。

《3.3 极化可编程阵列天线概念的验证》

3.3 极化可编程阵列天线概念的验证

为了验证本文提出的极化可编程阵列天线的概念,本文针对几个不同的期望极化,采用提出的精炼策略对16单元阵列的极化状态配置进行优化。值得一提的是,尽管设计的极化可重构天线单元只能实现8个不同的LP状态,但实际上其VAEP在16个工作状态之间是不同的。例如,当一个单元天线工作在0°或180°的极化状态时,可以认为它是处于同一个极化状态,不过这两种状态下天线的VAEP是不相同的。因为在这两种状态下,单元辐射的电磁场矢量及单元与其相邻单元之间的互耦都是不同的。因此,在阵列单元极化状态优化中,该单元天线被视作具有16种不同的极化状态。这16个极化状态的极化方位角分别为{0°, 22.5°, 45.0°,

下面展示第一个优化例子。当期望LP

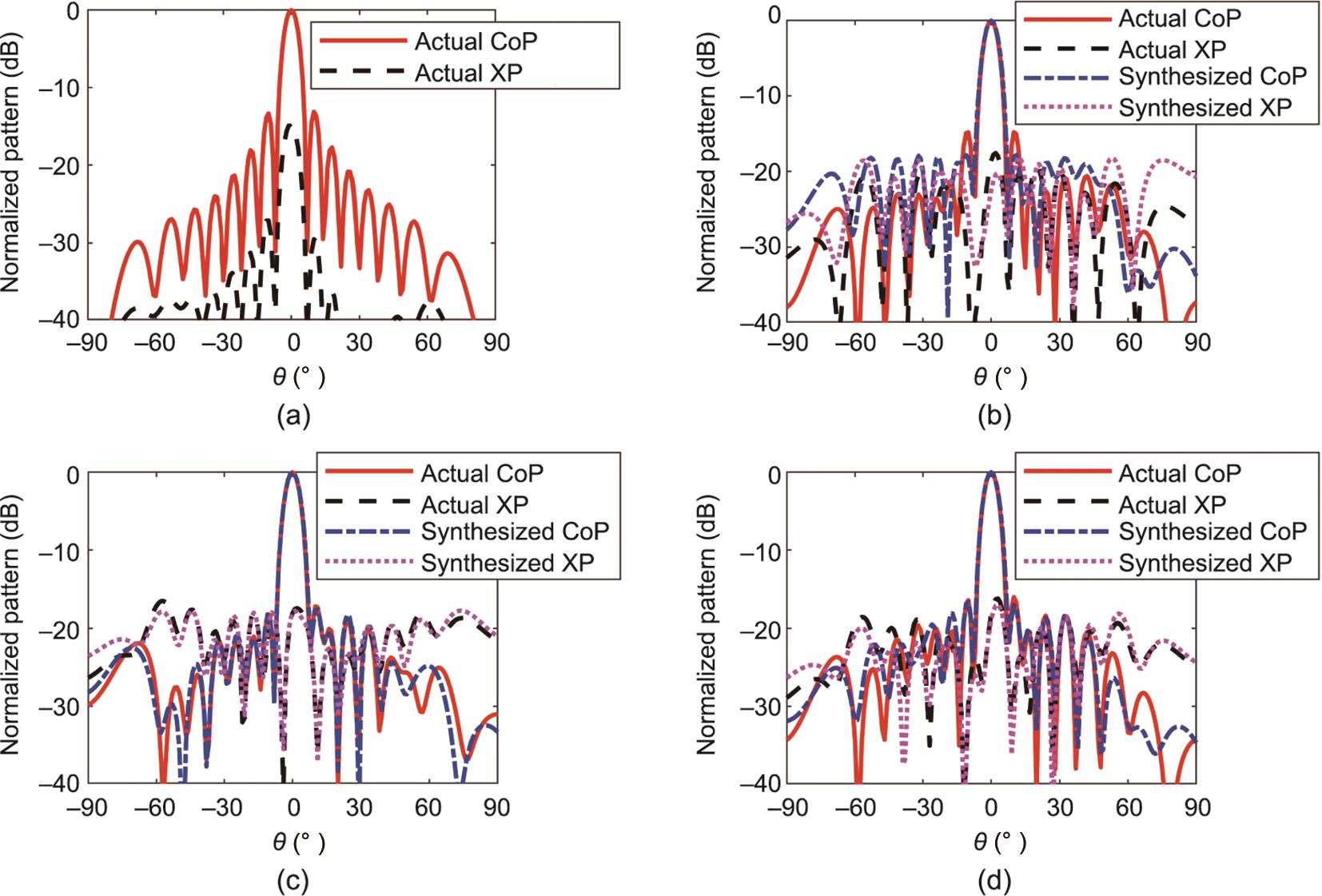

《图9》

图9 当期望极化为(90°, 30°)时,MLPR天线阵列在初始步骤和三个优化步骤的综合的方向图和由全波仿真得到的实际的方向图。(a)初始极化状态配置下的实际方向图;(b)第一优化步骤获得的方向图;(c)第二优化步骤获得的方向图;(d)第三优化步骤获得的方向图。

本研究为了释放更多的自由度来提高阵列方向图的性能,没有将阵列的极化状态配置限制为对称。在第一次优化获得的极化状态配置下工作的阵列的CoP和XP方向图如图9(b)所示。可见SLL为-17.88 dB,XPL为-17.92 dB,两者都非常接近期望值。然而,由于单元间互耦的变化,阵列在第一次优化获得的极化状态配置下的全波仿真方向图仅得到-14.96 dB的SLL和-16.80 dB的XPL。为了降低综合的和仿真的阵列方向图之间的差异,采用几个精炼步骤来再优化单元极化状态,如在算法中展示的那样。且随着精炼优化步数的增加,可选的极化状态范围被限制为逐渐缩小。本研究在第二和第三优化步骤中设置m2= 2和m3= 1(在第一个优化步骤中,每个单元可以选择所有的极化状态)。即将第n单元的可选偏振态范围设置为

《表1》

表1 当期望极化为(90°, 30°)时,提出的方法在初始步骤和三个优化步骤中获得的极化状态配置

| 16-element polarization state (° ) | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | |

| 0 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 |

| 1 | 22.5 | -45.0 | 67.5 | 22.5 | 45.0 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 45.0 | 22.5 | 45.0 | 0 | 67.5 | 22.5 |

| 2 | 45.0 | -22.5 | 22.5 | 22.5 | 45.0 | 22.5 | 22.5 | 22.5 | 22.5 | 22.5 | 45.0 | 22.5 | 67.5 | -45.0 | 90.0 | 22.5 |

| 3 | 45.0 | -22.5 | 22.5 | 22.5 | 45.0 | 22.5 | 22.5 | 22.5 | 45.0 | 22.5 | 45.0 | 22.5 | 90.0 | -45.0 | 90.0 | 0 |

《表2》

表2 当期望极化为(90°, 30°)时,MLPR天线阵列在初始步骤和三个优化步骤中综合和实际的阵列方向图的最大SLL和XPL

| Synthesized results (dB) | Simulated results (dB) | |||

|---|---|---|---|---|

| SLL | XPL | SLL | XPL | |

| 0 | ‒ | ‒ | -13.39 | -14.73 |

| 1 | -17.88 | -17.92 | -14.96 | -16.80 |

| 2 | -17.42 | -17.40 | -16.57 | -16.66 |

| 3 | -17.70 | -17.31 | -17.61 | -17.26 |

类似地,当期望的极化状态分别为(90°, 0°)、(90°, 45°)、(90°, 60°)和(90°, 90°)时,使用提出的精炼优化策略获得了合适的极化状态配置。其中,期望极化(90°, 60°)是单元天线本身无法单独实现的。与上述期望极化为(90°, 30°)的示例一样,可以采用本文提出的方法在约束SLL和XPL的情况下使阵列产生期望极化上的辐射。当期望极化为(90°, 0°)、(90°, 45°)和(90°, 90°)时,阵列可以将所有的单元的工作状态切换到相应的极化状态上以产生期望极化方向上的辐射。然而,这会导致阵列方向图具有约-13.5 dB的SLL。由于阵列单元之间存在互耦,真实情况的SLL甚至可能会更差。通过优化单元极化状态,可以降低该阵列的SLL。将在这4个期望极化下,通过提出的极化状态优化策略获得的综合的阵列方向图和仿真的阵列方向图展示在了图10(a)~(d)中,优化获得的阵列极化状态配置展示在了表3中,对应的SLL和XPL展示在了表4中。可见,在4个不同的期望LP下获得的仿真的阵列方向图的SLL和XPL均优于-16.5 dB。总的来说,虽然在本文中总共只考虑了5个LP的情况,但是可以得出结论,采用提出的单元极化状态优化策略,该MLPR天线阵列可以实现任意期望LP方向上的方向图,同时降低SLL和约束XPL。此外,由于提出的极化可编程阵列天线不涉及激励幅度和相位的优化,因此波束形成网络被大大简化。

《图10》

图10 MLPR天线阵列综合的CoP和XP方向图以及对应的由全波仿真获得的实际的方向图。(a)~(d)为在不同期望极化下获得的方向图:(a)(90°, 0°);(b)(90°, 45°);(c)(90°, 60°);(d)(90°, 90°)。

《表3》

表3 当期望极化为(90°, 0°)、(90°, 45°)、(90°, 60°)和(90°, 90°)时,由提出的优化策略获得的MLPR天线阵列的极化状态配置

| 16-element polarization state (°) | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | |

| (90°, 0°) | 0 | -45.0 | 0 | 0 | 22.5 | 0 | 0 | 0 | 0 | 0 | 0 | -22.5 | 45.0 | -90.0 | 90.0 | 0 |

| (90°, 45°) | 45.0 | 67.5 | 45.0 | 67.5 | 45.0 | 45.0 | 45.0 | 45.0 | 45.0 | 45.0 | 45 | 22.5 | 67.5 | -22.5 | 135.0 | 45.0 |

| (90°, 60°) | 67.5 | 45.0 | 67.5 | 67.5 | 67.5 | 67.5 | 67.5 | 67.5 | 67.5 | 67.5 | 45 | 67.5 | 0 | 45.0 | 157.5 | 67.5 |

| (90°, 90°) | 135.0 | 0 | 90.0 | -22.5 | 112.5 | 90.0 | 67.5 | 90.0 | 90.0 | 90.0 | 90 | 90.0 | 90.0 | 90.0 | 90.0 | 0 |

《表4》

表4 当期望的极化为(90°, 0°)、(90°, 45°)、(90°, 60°)和(90°, 90°)时,由提出的精炼优化策略得到的MLPR天线阵列方向图的SLL和XPL

| Synthesized results (dB) | Simulated results (dB) | |||

|---|---|---|---|---|

| SLL | XPL | SLL | XPL | |

| (90°, 0°) | -17.53 | -17.39 | -17.30 | -17.66 |

| (90°, 45°) | -17.07 | -17.90 | -17.00 | -17.81 |

| (90°, 60°) | -17.59 | -17.57 | -17.53 | -17.46 |

| (90°, 90°) | -17.04 | -17.52 | -16.53 | -16.76 |

《4、 实验结果》

4、 实验结果

本研究对上述阵列天线进行了加工和测试,以进一步验证极化可编程阵列天线的概念和提出的优化策略。加工得到的阵列天线原型的顶视图和底部视图展示在了图11(a)、(b)中。为了实现大规模的PIN二极管的通断控制和阵列极化的可编程,本文设计并加工了如图11(c)、(d)所示的基于FPGA的直流控制电路。单元天线的极化状态被4位二进制代码编码为{0000, 0001,

《图11》

图11 16单元MLPR天线阵列原型及其控制电路的照片。(a)阵列的俯视图(未完全组装);(b)阵列的底面视图;(c)阵列的FPGA控制板;(d)组装的极化可编程阵列。

《表5》

表5 当期望极化为(90°, 0°)、(90°, 30°)、(90°, 45°)、(90°, 60°)和(90°, 90°)时,得到的极化状态配置的二进制码

| Polarization state configuration codes | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | |

| (90°, 0°) | 0000 | 1101 | 0000 | 0000 | 0001 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 1110 | 0010 | 1010 | 0101 | 0000 |

| (90°, 30°) | 0010 | 1110 | 0001 | 0001 | 0010 | 0001 | 0001 | 0001 | 0010 | 0001 | 0010 | 0001 | 0101 | 1101 | 0101 | 0001 |

| (90°, 45°) | 0010 | 0011 | 0010 | 0011 | 0010 | 0010 | 0010 | 0010 | 0010 | 0010 | 0010 | 0001 | 0011 | 1110 | 0111 | 0010 |

| (90°, 60°) | 0011 | 0010 | 0011 | 0011 | 0011 | 0011 | 0011 | 0011 | 0011 | 0011 | 0010 | 0011 | 0000 | 0010 | 0111 | 0011 |

| (90°, 90°) | 0111 | 0000 | 0101 | 1110 | 0110 | 0101 | 0011 | 0101 | 0101 | 0101 | 0101 | 0101 | 0101 | 0101 | 0101 | 0000 |

《图12》

图12 不同期望极化下的MLPR天线阵列的测试和仿真的方向图。(a)(90°, 0°);(b)(90°, 30°);(c)(90°, 45°);(d)(90°, 60°);(e)(90°, 90°)。

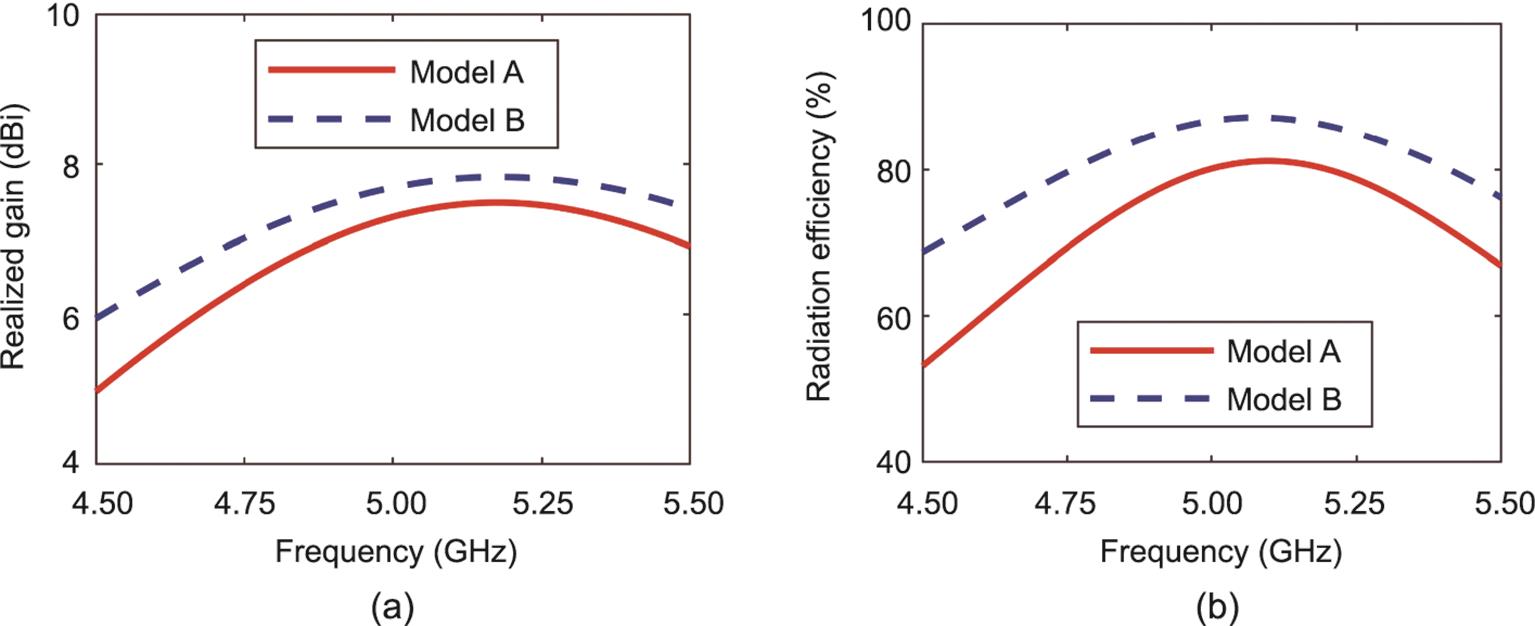

图13展示了阵列工作在上述5种优化的极化状态配置下时的仿真和测试的反射系数、增益曲线以及辐射效率。非均匀的单元极化状态分布可能会影响阵列的增益和带宽,因此在图13中还展示当全部单元极化状态分别为0°状态、45°状态和90°状态时的阵列的性能用作对比。这几个均匀的极化状态配置在图中分别记作均匀(90°, 0°)状态、均匀(90°, 45°)状态和均匀(90°, 90°)状态。从图13(a)中可见,MLPR天线阵列的反射系数在不同的极化状态配置下略有不同。阵列在不同状态下重叠的带宽约为8.6%,覆盖了4.77~5.20 GHz。需要注意的是,由于阵列的馈电网络是一个具有较宽带宽的并行网络,因此该阵列的带宽主要受使用的单元天线的限制。从图13(b)可知,与仿真的增益相比,阵列测试的增益降低了0.5~1 dB。在工作频段内,阵列在均匀(90°, 0°)状态、均匀(90°, 45°)状态和均匀(90°, 90°)状态下的实测增益范围为15.22~17.92 dBi,阵列在5个优化的极化状态配置下的实测增益范围为14.84~17.53 dBi。与均匀极化状态下的阵列增益相比,优化的极化状态配置下的阵列增益降低了0.4~0.7 dB。这是因为具有不同极化状态的单元天线辐射场之间会发生抵消,可能会对阵列的主极化增益产生负面影响。而MLPR天线阵列在均匀极化状态配置下将产生-13.5 dB的SLL。本文提出的方法为MLPR天线阵列提供了一种可选的极化状态配置,可用于降低其SLL。因此在实际应用中,如果可以接受少量的增益损失,那么可以采用优化的极化状态配置来降低阵列的SLL。如果-13.5 dB的SLL是可以接受的,则可以选择使用均匀的极化状态配置,以获取更高的增益。在工作波段内,阵列在优化的极化状态配置下的实测辐射效率为51.2%~62.64%,如图13(c)所示,这一指标略低于阵列处于均匀极化状态配置的情况。

《图13》

图13 MLPR天线阵列在5种优化极化状态配置和均匀(90°, 0°)状态、均匀(90°, 45°)状态和均匀(90°, 90°)状态下的测试和仿真的性能。(a)反射系数;(b)实际增益;(c)辐射效率。

值得注意是,虽然本研究只提供了以上5种不同期望极化的例子,但所提出的极化状态精炼优化策略可以使MLPR天线阵列产生任何期望LP上的方向图。这与已报道的大多数极化可重构天线阵列是不同的。如表7所示,已报道的极化可重构天线阵列主要包括右旋圆极化(RHCP)和左旋圆极化(LHCP)[32]、LP/CP [33‒34]和双LP [35‒36]可重构天线阵列,这些阵列只能实现少量的极化状态。据了解,本文首次报道了仅需等分功率分配器馈电的任意LP可重构阵列天线技术。此外,与参考文献[32‒35]中报道的阵列相比,本文提出的MLPR天线阵列可在没有激励幅度加权的情况下降低3~4 dB的SLL。而且提出的16单元天线阵列的增益均高于表7中的文献报道的16单元阵列。本研究采用了FPGA存储不同期望LP下优化获得的极化状态配置,因此,该MLPR天线阵列可根据实际应用中对阵列极化的要求,电控地切换到合适的极化状态配置上。

《表7》

表7 本文提出的阵列与已报道的极化可重构天线阵列之间的性能比较

| Ref. | Element antenna type | Number of elements | Feed network | Polarization states | Peak gain (dBi) | Maximum SLL (dB) | Maximum XPL (dB) | Overlapped frequency band (GHz) |

|---|---|---|---|---|---|---|---|---|

| [ | Polarization reconfigurable CP antenna | 4 × 4 | Single port | RHCP/LHCP | 15.50 | -11.20 | -13.00 | 2.53‒2.57 |

| [ | Ring slot substrate integrated waveguide cavity patch antenna | 2 × 2 | Power divider with 90° phase shifters | 0° LP, 90° LP, LHCP, RHCP | 10.30 | -11.00 | -20.00 | 5.30‒6.10 |

| [ | Microstrip antenna | 4 × 4 | Butler matrix | 0° LP, 90° LP, LHCP, RHCP | 14.50 | -12.00 | -16.30 | 5.00‒5.80 |

| [ | Reconfigurable aperture-fed patch antenna | 1 × 4 | Equal power divider | +45° LP, -45° LP | 13.50 | -12.50 | -10.00 | 2.25‒2.47 |

| [ | Dual-polarized slot-ring antenna | 2 × 2 | 10 Ports with transmitter and receiver modules | Dual LP | 2.40/3.10 | ‒ | -12.00 | 1.80‒3.70/4.50‒8.20 |

| This work | MLPR antenna | 1 × 16 | Equal power divider | Arbitrary LP | 17.34‒17.53 | -16.81‒-16.09 | -16.03 | 4.77‒5.20 |

《5、 讨论》

5、 讨论

如第2.1节所述,本研究提出的MLPR天线阵列有M个极化状态配置,其中M是单元的极化状态数目,N是阵列单元数目。因此,单元的极化数目越多或单元数量越大,阵列可能实现的极化状态配置就越多。这样,阵列就更有可能通过优化单元极化状态的方式在期望极化方向上获得更好的方向图性能。为了研究使用不同的N和M对实现的SLL和XPL的范围的影响,本文考虑几种不同的N和M组合的情况。为简化讨论,这里不考虑互耦的影响。这样一来,如2.2节所述,阵元极化状态的切换就相当于将阵元绕其中心旋转一定角度。此外,本研究选择采用旋转理想偶极天线的方向图来模拟不同极化状态下的单元方向图。因此,对于在

(15)

式中,

(16)

然后,使用方程(8)中的适应度函数和BGA来优化阵列的阵元极化状态配置。对于以下所有例子,设置期望的极化为(90°, 30°),优化目标为SLL = -20 dB和XPL = -20 dB。为了避免随机优化算法的偶然性,本研究对每种N和M的组合执行200次BGA优化。在图14中给出了当M = 4、6、8和10时,阵列在200次优化中实现的SLL、XPL和增益,其中单元数目固定为N = 16。如图14(a)所示,随着M从4变为8,获得的SLL逐渐降低。但是,当M从8增加到10时,阵列的SLL并没有得到太大改善。如图14(b)所示,阵列在M = 6时获得的XPL比在M = 4时低了约0.8 dB。当单元极化状态的数量M从6增加到8或10时,阵列的XPL并没有太大改善。从图14(c)可以看出,当M从4增加到8时,获得的增益提高了大约0.5 dB。在这些例子中,阵列在200次优化中获得的最佳SLL、XPL和增益分别为:M = 4时为-17.04 dB、-17.47 dB和14.37 dBi;M = 6时为-17.81 dB、-18.46 dB和14.72 dBi;M = 8时为-18.50 dB、-18.72 dB和14.80 dBi;M = 10时为-18.43 dB、-18.62 dB和14.82 dBi。图15给出了在N = 8、16和24时,阵列在200次优化中实现的SLL、XPL和增益,其中单元极化状态数目固定为M = 8。可以看出,当N从8增加到24时,阵列可以实现越来越好的SLL和XPL。同时,阵列的增益也随着单元数目的增加而提高。阵列在200次优化中获得的最佳SLL、XPL和增益分别为:N = 8时为-16.71 dB、-16.34 dB和11.80 dBi;N = 16时为-18.34 dB、-18.59 dB和14.80 dBi;N = 24时为-19.53 dB、-19.49 dB和16.73 dBi。把在不同N和M组合下阵列在200次优化中获得的最佳SLL、XPL和增益汇总在表8中,其中N和M的范围分别为[8, 16, 24]和[4, 6, 8, 10]。以上结果可作为读者在选用本文提出的方法时的一个参考。

《图14》

图14 当M = 4、6、8和10时,获得的SLL(a)、XPL(b)和增益(c),其中单元数量固定为N = 16。对于每个不同的M,都执行了200次BGA优化。

《图15》

图15 当N = 8、16和24时,获得的SLL(a)、XPL(b)和增益(c),单元极化状态数目固定为M = 8。对于每个不同的N,都执行了200次BGA优化。

《表8》

表8 在各种(, )组合下的200次BGA优化中获得的最佳SLL、XPL和增益

| SLL (dB), XPL (dB), gain (dBi) | ||||

|---|---|---|---|---|

| 8 | (-15.03, -16.45, 11.33) | (-16.45, -16.68, 11.81) | (-16.71, -16.34, 11.80) | (-16.54, -17.17, 11.79) |

| 16 | (-17.04, -17.47, 14.37) | (-17.81, -18.46, 14.72) | (-18.34, -18.59, 14.80) | (-18.43, -18.62, 14.82) |

| 24 | (-18.67, -18.70, 16.37) | (-19.33, -19.64, 16.78) | (-19.53, -19.49, 16.73) | (-19.71, -19.72, 16.75) |

《6、 总结》

6、 总结

本文提出了一款新颖的极化可编程阵列天线。该阵列由16个天线单元组成,每个天线单元具有8种可选的离散的极化状态,且由FPGA控制切换。通过有效的策略来获取近似天线的矢量方向图并用BGA优化单元极化状态配置,该阵列可以产生任何期望的LP上约束SLL和XPL的方向图。

京公网安备 11010502051620号

京公网安备 11010502051620号