#### Contents lists available at ScienceDirect

# Engineering

journal homepage: www.elsevier.com/locate/eng

Research MEMS Sensors—Article

# A MEMS Sensors Based on A Laterally Movable Gate Field-Effect Transistor (LMGFET) with A Novel Decoupling Sandwich Structure

Wendi Gao <sup>a,b,c,d</sup>, Zhixia Qiao <sup>e</sup>, Xiangguang Han <sup>a,b</sup>, Xiaozhang Wang <sup>a,b</sup>, Adnan Shakoor <sup>f,g</sup>, Cunlang Liu <sup>a</sup>, Dejiang Lu <sup>a,b,\*</sup>, Ping Yang <sup>a,b</sup>, Libo Zhao <sup>a,b,\*</sup>, Yonglu Wang <sup>a,b</sup>, Jiuhong Wang <sup>a,b</sup>, Zhuangde Jiang <sup>a,b</sup>,

- a State Key Laboratory for Manufacturing Systems Engineering, International Joint Laboratory for Micro/Nano Manufacturing and Measurement Technologies, Overseas Expertise Introduction Center for Micro/Nano Manufacturing and Nano Measurement Technologies Discipline Innovation, Xi'an Jiaotong University (Yantai) Research Institute for Intelligent Sensing Technology and System, School of Mechanical Engineering, Xi'an Jiaotong University, Xi'an 710049, China <sup>b</sup> Shandong Laboratory of Yantai Advanced Materials and Green Manufacturing, Yantai 265503, China

- <sup>c</sup> Beijing Advanced Innovation Center for Intelligent Robots and Systems, Beijing Institute of Technology, Beijing 100081, China

- <sup>d</sup> State Key Laboratory of Robotics and Systems, Harbin Institute of Technology, Harbin 150006, China

- <sup>e</sup> Eleventh Research Institute, Sixth Academy of China Aerospace Science and Technology Co., Xi'an 710100, China

- Department of Control and Instrumentation Engineering, King Fahd University of Petroleum and Minerals, Dhahran 31261, Saudi Arabia

- g Department of Biomedical Engineering, City University of Hong Kong, Hong Kong 999077, China

### ARTICLE INFO

Article history: Received 3 September 2021 Revised 8 March 2022 Accepted 5 June 2022 Available online 13 August 2022

Keywords: Force sensor Laterally movable gate Field-effect transistor Photoresistive SU-8 Biomedical micromanipulation

# ABSTRACT

This paper presents the development of a novel micro force sensor based on a laterally movable gate field-effect transistor (LMGFET). A precise electrical model is proposed for the performance evaluation of small-scale LMGFET devices and exhibits improved accuracy in comparison with previous models. A novel sandwich structure consisting of a gold cross-axis decoupling gate array layer and two soft photoresistive SU-8 layers is utilized. With the proposed dual-differential sensing configuration, the output current of the LMGFET lateral operation under vertical interference is largely eliminated, and the relative output error of the proposed sensor decreases from 4.53% (traditional differential configuration) to 0.01%. A practicable fabrication process is also developed and simulated for the proposed sensor. The proposed LMGFET-based force sensor exhibits a sensitivity of 4.65  $\mu A \cdot n N^{-1}$ , which is comparable with vertically movable gate field-effect transistor (VMGFET) devices, but has an improved nonlinearity of 0.78% and a larger measurement range of  $\pm 5.10 \,\mu N$ . These analyses provide a comprehensive design optimization of the electrical and structural parameters of LMGFET devices and demonstrate the proposed sensor's excellent force-sensing potential for biomedical micromanipulation applications.

© 2022 THE AUTHORS. Published by Elsevier LTD on behalf of Chinese Academy of Engineering and Higher Education Press Limited Company. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

## 1. Introduction

Micro-electromechanical system (MEMS) micro force sensors are efficient and necessary tools in many biomedical studies. Such tools have been used to measure the Young's modulus [1,2], viscosity [3,4], and locomotion traction [5] in living cells or tissues in order to study biological processes and biomedical reactions. Micro force sensors can provide precise force feedback in micro-robotic biomedical manipulations to improve the automation extent [6,7] and the survival rate of biological objects [8,9]. Recent studies

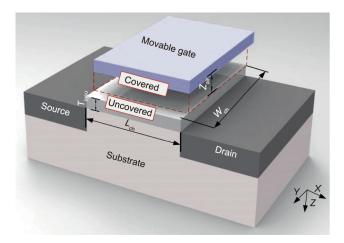

have focused on the organelle or molecular level, thereby increasing the demand for ultralow force sensing below the nanonewton level. Current force-sensing devices are mainly based on sensing principles, such as capacitive [10,11], piezoresistive [12,13], and piezoelectric [14,15] principles. The movable gate field-effect transistor (MGFET) force sensor exhibits several advantages over its competitors, such as a high sensitivity derived from the transistor array design [16,17], convenient signal amplification, and modulation with integrated circuits [18], thus making the on-chip measurement of low-scale forces feasible. Compared with traditional metal-oxide semiconductor field-effect transistors, MGFET devices have a floating gate over the substrate channel area and can move along three axes due to the air gap, as shown in Fig. 1. The current

https://doi.org/10.1016/j.eng.2022.06.018

2095-8099/© 2022 THE AUTHORS. Published by Elsevier LTD on behalf of Chinese Academy of Engineering and Higher Education Press Limited Company. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

<sup>\*</sup> Corresponding authors E-mail addresses: djlu@xjtu.edu.cn (D. Lu), libozhao@xjtu.edu.cn (L. Zhao).

**Fig. 1.** Sensing unit of the MGFET.  $T_{\text{insu}}$ : insulator thickness;  $L_{\text{ch}}$ : channel length;  $Z_{\text{air}}$ : air gap thickness;  $W_{\text{ch}}$ : whole channel width.

between the source and the drain electrodes reflects the applied external loads. In terms of the gate moving direction, MGFET devices are divided into two types: vertically MGFETs (VMGFETs) and laterally MGFETs (LMGFETs). VMGFETs exhibit high sensitivity, while their movement range is limited by the small air gap thickness. Their measurement linearity deteriorates with an increase in gate vertical deformation. Unexpected rapidly increased loads usually occur during biomedical measurements, such as during membrane penetration in biological cell microinjections [19,20], when the force amplitude increases sharply and may exceed the measurement range of a VMGFET device. In LMGFETs, the gate moves laterally along the channel width, and the air gap remains constant. The measurement range of LMGFETs is larger than that of VMGFETs, and their output current changes linearly during the measurement range. Therefore, a highly sensitive LMGFET force sensor is more versatile than a VMGFET in biomedical measurement.

Researchers have developed several MGFET devices on the basis of these two types, such as VMGFET-based accelerometers [21,22], differential amplifiers [23], and LMGFET-based displacement sensors [24]. Existing studies have found that the measuring sensitivity can be improved by scaling down the transistor size. However, the widely adopted long-channel model in Refs. [21-24], which ignores many scale effects, is inaccurate for describing MGFET performance, especially for devices with a small size. In our previous work, we proposed an accurate electrical model for small-scale VMGFET devices [25]. However, the movable gate of an LMGFET device partially covers the channel area, leaving the other part exposed. The operation behavior of LMGFET devices is relatively more complex than that of VMGFET devices, such that the previous VMGFET model is no longer applicable in LMGFET design. Therefore, a new precise electrical model is essential for the performance evaluation of small LMGFET devices. Moreover, the output current of an MGFET changes as its gate moves laterally and vertically, and loads from non-operation directions can produce considerable interference of output signals.

A differential sensing configuration has usually been adopted to attenuate the cross-axis coupling effect in MGFET devices [23,25]. However, this method is invalid for LMGFETs because the output current changes significantly when the gate moves vertically. The output change from lateral loads can be overwhelmed by vertical disturbances, producing undesirable measurement errors. Therefore, a novel decoupling movable structure and sensing configuration is required to improve sensing accuracy. The measuring sensitivity of MGFET devices can be further improved by lowering the stiffness of movable structures. In existing MGFET devices,

movable structures are made of rigid materials, such as silicon [21] and nickel [22,24] with large stiffness, such that the movable structure can hardly deform. One feasible method to improve the measuring sensitivity is to replace these stiff materials with other flexible alternatives. However, this is difficult for LMGFET devices, as they require high-aspect-ratio structures, and no such attempts have been conducted before.

The main contributions of this work are as follows. First, a separated channel-based electrical model is proposed to describe the operation behavior of small LMGFET devices, and its improved accuracy and capability for performance evaluation are demonstrated. Second, the electrical and structural parameters of LMGFET devices are fully analyzed to optimize the performance of ultralow force-sensing applications. Third, a flexible sandwich structure is proposed for the LMGFET micro force sensor, which consists of a gold cross-axis decoupling gate array layer and two soft photoresistive SU-8 layers. The sensor utilizes a novel dual-differential decoupling sensing configuration that exhibits excellent sensing sensitivity and anti-interference capability. Finally, the proposed LMGFET force sensor is simulated with a practicable fabrication process. The proposed sensor breaks through the limitation between the sensing accuracy and measurement range of MGFET devices. Its measuring sensitivity is 4.65 μA·nN<sup>-1</sup> for a large measurement range of  $\pm 5.10 \,\mu N$ , and its nonlinearity is less than 0.78%.

The rest of this paper is organized as follows: Section 2 models and analyzes the electrical behavior of the LMGFET. Section 3 illustrates the proposed LMGFET force sensor and describes the mechanical model and sensing configuration. Section 4 presents a practicable fabrication process for the proposed sensor. The theoretical model is then validated through simulation and experimental results, followed by a discussion of the sensor performance. Section 5 provides the conclusions.

# 2. Electrical modeling of the LMGFET

When the gate of an LMGFET moves laterally, the channel width changes such that the LMGFET can be divided into two separated parts-namely, a covered channel area with width  $W_{\mathrm{chc}}$  and an uncovered channel area with width  $W_{\rm chu}$  ( $W_{\rm chu}$  =  $W_{\rm ch}$  -  $W_{\rm chc}$ ) (where  $W_{ch}$  is the whole channel width). The two parts share some common parameters, such as the channel length  $L_{ch}$ , voltage difference between the gate and source electrode  $V_{\rm gs}$ , and voltage difference between the drain and source electrode  $V_{ds}$ . Due to the difference in the gate modulation effect at different lateral positions, the electron conductance in each channel area differs significantly. The whole channel exhibits several individual electrical parameters, such as the gate capacitance  $C'_{\rm eff}$ , carrier mobility  $U'_{eff}$ , and channel current  $I_{ds}$ . Thus, an investigation of the electrical parameters in each part is necessary in order to understand the operation principles of the LMGFET. Such an investigation is conducted in this section.

# 2.1. Effective gate capacitance

The capacitance between the gate and the covered and uncovered channel area changes when the gate moves laterally. Gate capacitance is a parameter describing the capacitance over a unit area. More specifically, the effective gate capacitance in the covered channel area  $C_{\rm effc}$  is the series capacitance of the air gap and gate insulator, which can be expressed as follows:

$$C'_{\text{effc}} = \frac{\varepsilon_0}{\frac{\varepsilon_0 T_{\text{insu}}}{\varepsilon_{\text{insu}}} + Z_{\text{air}}} = \frac{\varepsilon_0}{Z'_{\text{effc}}}$$

(1)

where  $\varepsilon_0$  = 8.854  $\times$  10<sup>-14</sup> F·cm<sup>-1</sup> is the permittivity of air;  $\varepsilon_{\rm insu}$  is the permittivity of the insulator;  $Z_{\rm air}$  is the air gap thickness;  $T_{\rm insu}$

is the insulator thickness; and  $Z'_{\rm effc}$  is the effective gate gap thickness in the covered area. A previous study assumed that the effective gate capacitance in the uncovered channel area  $C'_{\rm effu}$  is constant during gate movement [24]; however, this assumption is not in accordance with reality and can cause many artifacts in the device performance estimation. In this study, we propose an accurate variable expression of  $C'_{\rm effu}$  based on the fringe parasitic effect of the gate sidewall and bottom line [26,27]:

$$C'_{\text{effu}} = \frac{2\varepsilon_0}{\pi W_{\text{chu}}} \ln \left[ \frac{Z'_{\text{effc}} + T'_{\text{g}} + \sqrt{{T'_{\text{g}}}^2 + 2T'_{\text{g}} Z'_{\text{effc}}}}{Z'_{\text{effc}}} \right] + \frac{k\varepsilon_0}{\pi W_{\text{chu}} L_{\text{ch}}} \ln \left[ \frac{\pi L_{\text{ch}}}{Z'_{\text{effc}}} \right]$$

$$= \frac{\varepsilon_0}{Z'_{\text{effu}}}$$

(2

where  $T_{\rm g}' = T_{\rm g} {\rm e}^{\left(\frac{\pi W_{\rm chu} - \sqrt{{T_{\rm g}}^2 + 2T_{\rm g} Z_{\rm effc}'}}{\beta Z_{\rm effc}'}\right)}$  is the effective gate thickness for the sidewall parasitic capacitance;  $T_{\rm g}$  is the gate thickness; k and  $\beta$  are fitting parameters; and  $Z_{\rm effu}'$  is the effective gate gap thickness in the uncovered area.

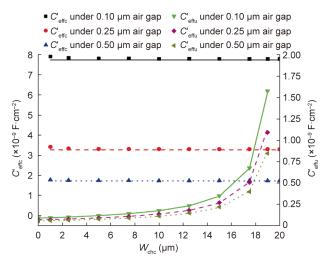

The effective gate capacitance of the two separated areas is examined at different lateral and height positions and compared with simulation results from the finite-element method (FEM) software Ansoft Maxwell. In this calculation, the whole channel width  $W_{\rm ch}$  is 20  $\mu$ m; the air gap thickness  $Z_{\rm air}$  is from 0.1 to 0.5  $\mu$ m; the gate thickness  $T_{\rm g}$  is 0.2  $\mu$ m; the gate insulator is silicon nitride, and its thickness  $T_{\text{insu}}$  is 100 nm; and the channel length  $L_{\text{ch}}$  is 5  $\mu$ m. During gate movement, most of the electric potential is concentrated in the covered area, and a small amount is scattered on the boundary edge because of the fringe parasitic effect. The effective gate capacitance in the covered channel area  $C'_{\text{effc}}$  remains almost constant at full width. As the covered area width  $W_{\mathrm{chc}}$  approaches zero, the scattered potential proportion increases, and  $C'_{\rm effc}$  experiences a small increase, as shown by the dots in Fig. 2. However, the relative error of  $C'_{effc}$  between the model and the simulation results is less than 3.0% for a small  $W_{\rm chc}$  of 1  $\mu m$  in three different air gaps. The value of the effective gate capacitance in the uncovered channel area  $C'_{effu}$  is one order less than that of  $C'_{effc}$ . The gate capacitance in the uncovered area mainly results from the scattered electric potential in the gate sidewall and bottom line. The total electrical potential

**Fig. 2.** Relationship between the effective gate capacitances  $C'_{\rm effc}$  and  $C'_{\rm effu}$ , and the channel width at different air gaps. Lines represent the calculated capacitance, while scatters are the simulated results.

remains constant, but the size of the uncovered area changes during gate movement.  $C_{\rm effu}'$  exhibits an inversely proportional relationship with width in the covered area  $W_{\rm chc}$ . When  $W_{\rm chc}$  is low,  $C_{\rm effu}'$  increases slowly because the change in  $W_{\rm chu}$  is insignificant. However, the size of the uncovered area changes greatly as  $W_{\rm chc}$  approaches the whole channel width, resulting in a rapid increase of  $C_{\rm effu}'$ . The scattered electrical potential increases as the air gap  $Z_{\rm air}$  decreases and then aggravates this phenomenon. The calculation of  $C_{\rm effu}'$  also shows an excellent coincidence with the simulated results, where the largest relative error is less than 3.5%.

## 2.2. Threshold voltage

Threshold voltage is a crucial switch parameter modulating the current channel between the source and drain electrodes. The channel current exists only if the gate voltage is larger than the threshold voltage for an accumulation-type MGFET. For a depletion-type device, in which the channel current is originally induced, a gate voltage approaching the threshold value can break off the conducting channel. The covered and uncovered channel areas have different threshold voltages, so they can have different channel statuses during lateral and vertical gate movement. Considering the short and narrow channel effects, the threshold voltages in the two areas are modeled separately, as follows:

$$V_{thc} = \varphi_{MS} + \varphi_{B} \pm F_{S} \frac{Z'_{effc} \sqrt{|2qN_{a/d}\varepsilon_{si}(\varphi_{B} - V_{bs})|}}{\varepsilon_{0}} \mp \frac{Q'_{eff}Z'_{effc}}{\varepsilon_{0}} + F_{Nc}(\varphi_{B} - V_{bs})$$

(3)

$$\begin{split} V_{thu} &= \varphi_{\text{MS}} + \varphi_{\text{B}} \pm F_{\text{S}} \frac{Z'_{\text{effu}} \sqrt{|2qN_{\text{a/d}}\varepsilon_{\text{si}}(\varphi_{\text{B}} - V_{\text{bs}})|}}{\varepsilon_{0}} \mp \frac{Q'_{\text{eff}}Z'_{\text{effu}}}{\varepsilon_{0}} \\ &+ F_{\text{Nu}}(\varphi_{\text{B}} - V_{\text{bs}}) \end{split} \tag{4}$$

where  $\varphi_{\rm MS}$  is the work function difference between the gate and channel;  $\varphi_{\rm B}$  is the channel built-in voltage, which is  $\frac{k_{\rm B}T}{q}\ln\left(\frac{N_{\rm a}}{n_{\rm i}^2}\right)$

and  $-\frac{k_{\rm B}T}{q}\ln\left(\frac{N_{\rm d}}{n_{\rm i}^2}\right)$  for an N-channel device and a P-channel device,

respectively;  $N_{\rm a/d}$  is the net concentration of ionized acceptors in a P-type substrate and donors in an N-type substrate, respectively;  $q=1.6\times 10^{-19}\,\rm C$  is the magnitude of the electron or hole charge,  $n_{\rm i}$  is the intrinsic doping concentration of silicon,  $k_{\rm B}$  is the Boltzmann constant, and T is the thermodynamic temperature;  $\varepsilon_{\rm si}$  is the permittivity of silicon;  $V_{\rm bs}$  is the voltage difference between the source and substrate electrodes;  $Q_{\rm eff}'$  is the effective charge density of the channel, where the minus and plus signs are respectively for N-channel and P-channel devices; and  $F_{\rm S}$  is the channel length coefficient, which is expressed as follows:

$$F_{S} = 1 - \frac{X_{j} \left[ a + d_{0} + d_{1} \frac{\sqrt{\frac{|2\varepsilon_{si}(\varphi_{B} - V_{bs})|}{qN_{a}}}}{X_{j}} + d_{2} \left( \frac{\sqrt{\frac{|2\varepsilon_{si}(\varphi_{B} - V_{bs})|}{qN_{a}}}}{X_{j}} \right)^{2} \right]}{L_{ch}} \times \sqrt{1 - \left( \frac{\sqrt{\frac{|2\varepsilon_{si}(\varphi_{B} - V_{bs})|}{qN_{a}}}}{X_{j} + \sqrt{\frac{|2\varepsilon_{si}(\varphi_{B} - V_{bs})|}{qN_{a}}}}}{X_{j} + \sqrt{\frac{|2\varepsilon_{si}(\varphi_{B} - V_{bs})|}{qN_{a}}}} \right)^{2} - \frac{aX_{j}}{L_{ch}}}$$

(5)

where  $X_j$  is the depth of the P—N junctions in the source or the drain electrode; and a,  $d_0$ ,  $d_1$ , and  $d_2$  are model parameters.  $F_{Nc}$  and  $F_{Nu}$  are the channel width coefficients in the covered and uncovered channel areas, respectively, and are expressed as follows:

$$F_{Nc} = \frac{\delta \pi \varepsilon_{si} Z'_{effc}}{4W_{chc} \varepsilon_0} \tag{6}$$

$$F_{\text{Nu}} = \frac{\delta \pi \varepsilon_{\text{si}} Z'_{\text{effu}}}{4 W_{\text{chu}} \varepsilon_0} \tag{7}$$

where  $\delta$  is the channel width model factor. The positive sign before the  $F_S$  term is for an N-channel device while negative sign is for a P-channel device. The sign before the  $Q'_{\rm eff}$  term is opposite compared with that before the  $F_S$  term, and the difference between the  $F_S$  and the  $Q'_{\rm eff}$  term can primarily determine the value of the threshold voltage. For example, a large  $Q'_{\rm eff}$  term can result in a negative threshold voltage for a depletion-type MGFET device with a P-type substrate (Fig. 3).

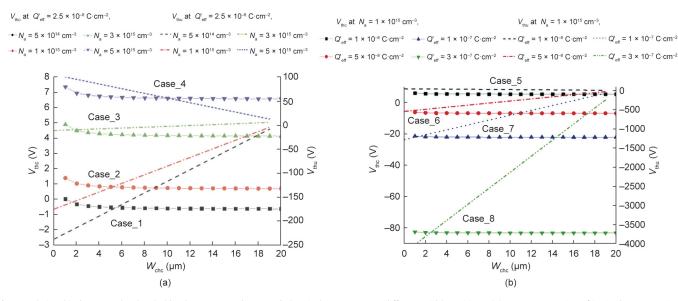

Although the channel length coefficient  $F_S$  remains constant, the channel width coefficient changes during lateral and vertical gate movements, especially for the uncovered channel area, whose effective gate gap  $Z'_{effu}$  varies significantly at different positions. Therefore, the threshold voltage will exhibit different characteristics in the two channel areas and needs comprehensive analysis. The effective charge density of the channel  $Q'_{eff}$  and the substrate concentration  $N_{a/d}$  are studied first. A P-type substrate device is adopted as an example, with the following parameters: The channel width  $W_{\rm ch}$  is 20 µm, the air gap  $Z_{\rm air}$  is 0.25 µm, the channel length  $L_{\rm ch}$  is 5  $\mu$ m, the P–N junction depth  $X_{\rm j}$  is 0.5  $\mu$ m, the intrinsic doping concentration  $n_i$  is  $1.5 \times 10^{10}$  cm<sup>-3</sup>, the implanted model constant a = 0.04,  $d_0 = 0.0631353$ ,  $d_1 = 0.8013292$ ,  $d_2 =$ 0.01110777, the work function voltage difference  $\varphi_{\rm MS}$  = 3.83 V, and the voltage difference between the substrate and the source electrode  $V_{\rm bs}$  = 0 V. The remaining parameters are the same as those given in Section 2.1. The effect of the substrate acceptor concentration  $N_a$  is investigated from Case\_1 to Case\_4 in Table 1, where  $N_a$  increases from 5  $\times$  10<sup>14</sup> to 5  $\times$  10<sup>15</sup> cm<sup>-3</sup>, while  $Q'_{eff}$  is kept low at  $2.5 \times 10^{-8}$  C·cm<sup>-2</sup>. For a small  $N_a$  in Case\_1, both parts behave as depletion-type transistors, and the channel is initially conductive because their energy band has been bent by dominant electrons in the channel surface. To break off the conducting channel, a negative threshold voltage is required to attract holes in the substrate. However,  $V_{\rm thc}$  becomes positive while  $V_{\rm thu}$  remains negative when  $N_a$  increases to  $1.0 \times 10^{15} \, \mathrm{cm}^{-3}$ ; the covered part becomes an accumulation-type transistor, and the uncovered part remains a depletion type in Case\_2. Because of its flat energy band,

**Table 1**Threshold voltage of covered/uncovered channel area under different electrical parameters

| Case | $N_{\rm a}~({\rm cm}^{-3})$ | $Q'_{eff}(C \cdot cm^{-2})$ | $V_{\rm thc} (V)^{\rm a}$ | $V_{\mathrm{thu}}\left(V\right)^{\mathrm{b}}$ |

|------|-----------------------------|-----------------------------|---------------------------|-----------------------------------------------|

| 1    | $5 \times 10^{14}$          | $2.5 \times 10^{-8}$        | _                         | _                                             |

| 2    | $1 \times 10^{15}$          | $2.5 \times 10^{-8}$        | +                         | _                                             |

| 3    | $3 \times 10^{15}$          | $2.5 \times 10^{-8}$        | +                         | _/+                                           |

| 4    | $5 \times 10^{15}$          | $2.5 \times 10^{-8}$        | +                         | +                                             |

| 5    | $1 \times 10^{15}$          | $1.0 \times 10^{-8}$        | +                         | _                                             |

| 6    | $1 \times 10^{15}$          | $5.0 \times 10^{-8}$        | _                         | _                                             |

| 7    | $1 \times 10^{15}$          | $1.0 \times 10^{-7}$        | _                         | _                                             |

| 8    | $1 \times 10^{15}$          | $3.0 \times 10^{-7}$        | _                         | _                                             |

<sup>&</sup>lt;sup>a</sup> "+" and "–" refer to accumulation and depletion types, respectively.

the channel in the covered area is not conductive until the inversion layer is formed, wherein holes gather in the channel surface under electrical potential forces resulting from a positive threshold voltage  $V_{\rm thc}$ . This condition appears to be desirable for device design, because the uncovered part with a nonlinear effective gate capacitance can be eliminated. However, it results in poor device performance, as only the covered part contributes to the output current.

During LMGFET operation,  $V_{\rm thc}$  decreases moderately and  $V_{\rm thu}$  increases sharply as  $W_{\rm chc}$  increases, indicating that  $V_{\rm thu}$  is more susceptible to channel width modulation. More specifically,  $V_{\rm thu}$  changes from -0.817 V at a  $W_{\rm chc}$  of 13 µm to 0.074 V at a  $W_{\rm chc}$  of 14 µm in Case\_3. This condition can make the uncovered area change from a depletion type to an accumulation type during operation and should be avoided. When  $N_{\rm a}$  increases above  $5\times 10^{15}$  cm<sup>-3</sup>, the two areas become accumulation types in Case\_4. The effect of the channel's effective charge density  $Q'_{\rm eff}$  is then investigated from Case\_5 to Case\_8, where  $Q'_{\rm eff}$  increases from  $1\times 10^{-8}$  to  $3\times 10^{-7}$  C·cm<sup>-2</sup>. In these cases,  $N_{\rm a}$  is kept at  $5\times 10^{15}$  cm<sup>-3</sup>, a value that is commonly available using commercial silicon wafers. For a low  $Q'_{\rm eff}$  of  $1\times 10^{-8}$  C·cm<sup>-2</sup> in Case\_5, the covered part behaves as an accumulation-type transistor, while the uncovered part is a depletion type. Holes become dominant as  $Q'_{\rm eff}$

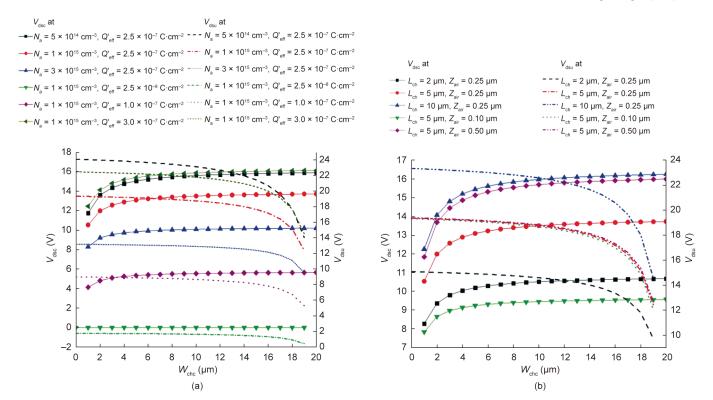

Fig. 3. Relationship between the threshold voltages  $V_{\text{thc}}$  and  $V_{\text{thu}}$ , and electrical parameters at different width positions. (a) Net concentration of ionized acceptors in the substrate  $N_{\text{a}}$ ; (b) effective channel charge density  $Q'_{\text{eff}}$ . Symbol lines indicate the threshold voltage in the covered channel area  $V_{\text{thc}}$ , and dotted lines indicate the threshold voltage in the covered channel area  $V_{\text{thc}}$  and dotted lines indicate the threshold voltage in the covered channel area  $V_{\text{thu}}$ . Case\_1-Case\_4:  $N_{\text{a}}$  increases from  $5 \times 10^{14}$  to  $5 \times 10^{15}$  cm<sup>-3</sup>, while  $Q'_{\text{eff}}$  is kept low at  $2.5 \times 10^{-8}$  C·cm<sup>-2</sup>; Case\_5-Case\_8:  $Q'_{\text{eff}}$  increases from  $1 \times 10^{-8}$  to  $3 \times 10^{-7}$  C·cm<sup>-2</sup>, while  $N_{\text{a}}$  is kept at  $1 \times 10^{15}$  cm<sup>-3</sup>.

b "-/+" indicates that the device changes from a depletion to accumulation type.

increases above 5  $\times$   $10^{-8}\,\text{C}\cdot\text{cm}^{-2},$  allowing both areas to function as depletion-type transistors.

The relationship between the threshold voltage  $V_{\rm th}$  and the geometry parameters  $L_{\rm ch}$  and  $Z_{\rm air}$  is shown in Fig. 4, where  $N_{\rm a}$  and  $Q_{\rm eff}'$  are set at 1  $\times$  10<sup>14</sup> cm<sup>-3</sup> and 2.5  $\times$  10<sup>-7</sup> C·cm<sup>-2</sup>, respectively.  $V_{\text{thc}}$  has a strong negative correlation with the air gap  $Z_{\text{air}}$ as the effective gate height  $Z_{\rm effc}^\prime$  increases. However,  $V_{\rm thc}$  rarely changes for different channel lengths  $L_{\rm ch}$ .  $V_{\rm thu}$  increases slowly with an increase in channel length  $L_{ch}$ , but decreases significantly with an increase in the air gap  $Z_{air}$  for the same reason as  $V_{thc}$ . Therefore, the desired working types are achievable through appropriate assignment of electrical and geometry parameters. A nonzero gate voltage inducing a conducting channel in an accumulation-type device can probably produce an electrostatic force between the movable gate and substrate, resulting in undesirable vertical interference during operation [28]. The channel of a depletion-type device is conducted, although the potential difference is zero. Thus, electrostatic forces are eliminated. In other words, a depletion type is strongly expected for LMGFET devices. Therefore, the following design analysis is based on the norm that an LMGFET is free from electrostatic forces with a fixed gate voltage of 0 V.

## 2.3. Output channel current

The surface current density in two channel areas differs from each other. Thus, the current between the drain and source electrode in each area should be calculated individually, and the total output current should be their sum. By integrating the density of the channel surface carriers between two electrodes [29], the output current in the covered area  $I_{\rm dsc}$  and the output current in the uncovered area  $I_{\rm dsu}$  are defined as follows:

$$I_{\rm dsc} = \frac{W_{\rm chc}\mu'_{\rm effc}Z'_{\rm effc}}{L_{\rm ch}\varepsilon_0} \left(V_{\rm gs} - V_{\rm thc} - \frac{1 + F_{\rm Bc}}{2}V_{\rm ds}\right)V_{\rm ds} \tag{8}$$

$$I_{\rm dsu} = \frac{W_{\rm chu}\mu_{\rm effu}'Z'_{\rm effu}}{L_{\rm ch}\varepsilon_0} \bigg(V_{\rm gs} - V_{\rm thu} - \frac{1+F_{\rm Bu}}{2}V_{\rm ds}\bigg)V_{\rm ds} \tag{9}$$

**Fig. 4.** Relationship between the threshold voltage  $V_{\rm th}$  and the geometry parameters  $L_{\rm ch}$  and  $Z_{\rm air}$  at different width positions.

where  $F_{\rm Bc/u} = \frac{F_{\rm S}\sqrt{2qN_{\rm a}\varepsilon_{\rm si}}}{4\sqrt{|\varphi_{\rm B}-V_{\rm bs}|}} + F_{\rm Nc/u}$  is a voltage modulation coeffi-

cient in the covered and uncovered areas;  $\mu'_{\rm effc}$  and  $\mu'_{\rm effu}$  are the effective carrier mobilities in the covered and uncovered areas, respectively, which can be expressed as follows:

$$\mu'_{\text{effc}} = \frac{\mu_0}{1 + \frac{\delta}{Z'_{\text{effc}}} (V_{\text{gs}} - V_{\text{thc}}) + \frac{\mu_0}{V_{\text{max}} L_{\text{ch}}} V_{\text{ds}}}$$

(10)

$$\mu'_{\rm effu} = \frac{\mu_0}{1 + \frac{\delta}{Z'_{\rm effu}} (V_{\rm gs} - V_{\rm thu}) + \frac{\mu_0}{V_{\rm max} L_{\rm ch}} V_{\rm ds}} \tag{11}$$

where  $\mu_0$  is the surface mobility of the carriers at a low electric field;  $\delta$  is the vertical potential field factor; and  $V_{\rm max}$  is the saturated velocity of the carriers. Effective carrier mobility is mainly regulated

by the term  $\frac{\delta}{Z_{effu/c}'}(V_{gs}-V_{thu/c})$ , which accounts for the vertical

potential degrading effect, and by the term  $\frac{\mu_0}{V_{\rm max}L_{\rm ch}}V_{\rm ds}$ , which describes the velocity limitation and lateral potential degrading effect [30].  $\mu'_{\rm effc}$  and  $\mu'_{\rm effu}$  change when the gate shifts to different channel widths and heights.  $I_{\rm ds}$  approaches the value of the saturated current  $I_{\rm dsat}$  when  $V_{\rm ds}$  increases to a saturated status.

As discussed in our previous work [25], the saturated voltage of small-scale devices results from a saturated velocity. The saturated voltages in the covered area  $V_{\rm dsatc}$  and in the uncovered channel area  $V_{\rm dsatu}$  are expressed as follows:

$$V_{\text{dsatc}} = \frac{V_{\text{gs}} - V_{\text{thc}}}{1 + F_{\text{Bc}}} + \frac{V_{\text{max}} L_{\text{ch}}}{\mu'_{\text{effc}}} - \sqrt{\left(\frac{V_{\text{gs}} - V_{\text{thc}}}{1 + F_{\text{Bc}}}\right)^2 + \left(\frac{V_{\text{max}} L_{\text{ch}}}{\mu'_{\text{effc}}}\right)^2}$$

(12)

$$V_{\rm dsatu} = \frac{V_{\rm gs} - V_{\rm thu}}{1 + F_{\rm B}} + \frac{V_{\rm max} L_{\rm ch}}{\mu'_{\rm effu}} - \sqrt{\left(\frac{V_{\rm gs} - V_{\rm thu}}{1 + F_{\rm Bu}}\right)^2 + \left(\frac{V_{\rm max} L_{\rm ch}}{\mu'_{\rm eff}}\right)^2}$$

(13)

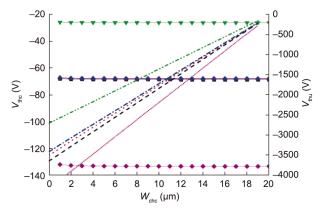

where  $I_{dsat}$  is the maximum controllable output for LMGFET devices and is directly affected by the threshold voltage applied at the drain electrode. Fig. 5 illustrates the relationship between the threshold voltage in the two areas and the electrical parameters (with acceptor concentration  $N_a$  and effective channel charge density  $Q'_{eff}$ ) and geometrical parameters (with air gap  $Z_{air}$  and channel length  $L_{ch}$ ). Aside from the similar parameters in the last calculation, the voltage difference between the substrate and source electrode  $V_{\rm gs}$  is 0 V, the carrier surface mobility  $\mu_0$  is 700 cm $^2 \cdot V^{-1} \cdot s^{-1}$  [31], and the saturated velocity  $V_{\rm max}$  is 8  $\times$  10<sup>6</sup> cm·s<sup>-1</sup> [32]. The saturated voltages of the two areas decrease with an increase in  $N_a$  and  $Q'_{eff}$ ; they also decrease with a decrease in the corresponding channel width ( $W_{\rm chc}/W_{\rm chu}$ ). More specifically, the decreasing amplitude due to a small width becomes distinct with an increase in  $N_a$  and  $Q'_{eff}$ . The green lines in Fig. 5(a) correspond to Case\_2 in Table 1. The covered channel area is currently broken off, so the saturated voltage in the covered area is 0. The geometric parameters exhibit an opposite influence to the electrical ones.  $V_{dsatc}$  increases with an increase in  $L_{\rm ch}$  and  $Z_{\rm air}$ , as shown in Fig. 5(b).  $V_{\rm dsatu}$  increases with an increase in  $L_{ch}$  and is insensitive to the change in the air gap  $Z_{air}$ . For a channel width  $W_{\rm chu}$  of 10  $\mu m$ ,  $V_{\rm dsatu}$  only changes by 0.18 V when  $Z_{\rm air}$  changes from 0.1 to 0.5 µm.

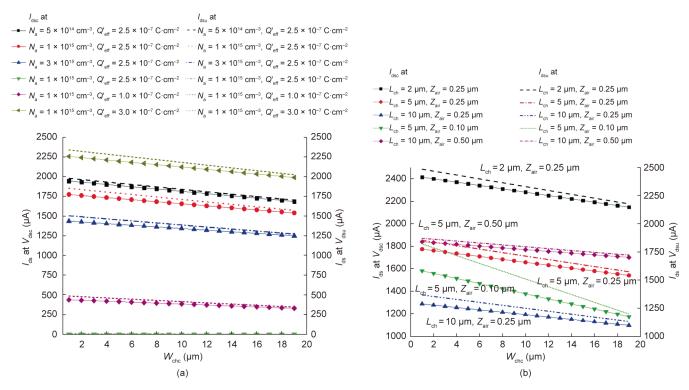

The adopted saturated voltage is set to the lowest value during the gate's lateral movement to analyze the saturated current. The current  $I_{\rm ds}$  is assumed to be constant if the applied voltage exceeds the saturated value in each area. A large  $Q'_{\rm eff}$  or lower  $N_{\rm a}$  results in a large  $I_{\rm dsat}$  in two areas due to the large absolute value of the threshold voltages  $V_{\rm thc}$  and  $V_{\rm thu}$ . The saturated current is approximately zero when only the uncovered channel works in this case, as shown by the green lines of Fig. 6(a). The deformation sensitivity

Fig. 5. Relationship between the saturated voltages  $V_{\rm dsc}$  and  $V_{\rm dsu}$ , and the electrical parameters and geometry parameters at different width positions. (a) Doped concentration of substrate  $N_a$  with effective channel charge density  $Q'_{\rm eff}$ ; (b) channel length  $L_{\rm ch}$  and air gap  $Z_{\rm air}$ .  $L_{\rm ch}$  is 5 μm and  $Z_{\rm air}$  is 0.25 μm for (a), while  $Q'_{\rm eff}$  is 2.5 × 10<sup>-8</sup> C·cm<sup>-2</sup> and  $N_a$  is 1 × 10<sup>15</sup> cm<sup>-3</sup> for (b).

S is defined as the slope of the channel current curves and can be used to evaluate the electrical performance of the device when the gate moves laterally. The sensitivity S improves with an increase in the channel length  $L_{\rm ch}$ . For an air gap  $Z_{\rm air}$  of 0.25  $\mu m$ , S increases from 13.144 to 17.140  $\mu A \mu m^{-1}$  when  $L_{ch}$  decreases from 10 to 2 µm. However, the device operation stability should be considered, because a small device size can result in a large potential field between the drain and source electrode and can easily break down the device. The air gap  $Z_{air}$  has a very large effect on the channel current  $I_{\rm ds}$  and sensitivity S. For the device with a channel width  $W_{\rm ch}$  of 10  $\mu m$  and a channel length of 5  $\mu m$ , the channel current  $I_{ds}$  increases from 1509.744 to 1796.400  $\mu A$  when Z<sub>air</sub> decreases from 0.5 to 0.1 μm. However, S decreases from 34.634 to 8.314  $\mu$ A· $\mu$ m<sup>-1</sup> during this period, as shown in Fig. 6(b). This condition indicates that the output produced from undesirable vertical movement can be several times greater the current change from lateral movement. Therefore, a decoupling design is required to eliminate the interference from vertical movement, as discussed in the next section.

# ${\bf 3. \ Sensor \ design \ and \ interconnection \ configuration}$

The proposed sensor utilizes an epoxy-type polymer photoresist, SU-8, as the structural material, which is an ideal material to fabricate LMGFET devices for the following reasons: First, SU-8 has a relatively low elastic modulus of 4–5 GPa, high mechanical strength, and stable chemical stability after ultraviolet (UV) exposure [33,34]. Second, SU-8 is a negative thick-film photoresist and can be used fabricate structures with a high aspect ratio [35]. These features make SU-8 suitable to serve as the structural material of laterally movable structures. Third, it is easy to uniformly deposit SU-8 on the substrate by utilizing a spin-coater or spray-coater, even for unleveled surfaces [36]. Finally, SU-8 can be easily pat-

terned by UV exposure and developed in a propylene glycol methyl ether acetate solution, which is very much considerably more operable than etching materials, such as metal and silicon. In this research, an SU-8-based LMGFET force sensor with a movable sandwich structure is proposed, as discussed in the following section.

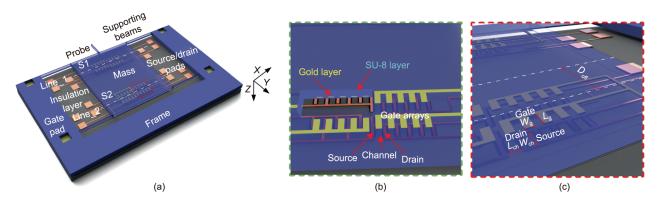

# 3.1. Movable structure design

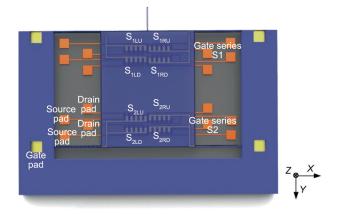

The movable structure and the substrate are two main components in the device, as shown in Fig. 7(a). The movable structure contains a probe and a center mass supported by straight beams. Fig. 7(b) shows the sandwich gate structure in which a gold gate electrode layer is fully covered by two photoresistive SU-8 layers. Gold is a common metal material in most labs and has been demonstrated to have excellent adhesion to SU-8 [37]. The thickness of the lower SU-8 structural layer should be small in order to decrease the effective gate gap and effective capacitance. Two series of gold gate arrays, S1 and S2, are set in the center mass with an offset distance  $D_{\text{off}}$ . In each series, two gate arrays lie symmetrically about with respect to the lateral lines Line\_1 and Line\_2. The gates in two series have the same width  $W_g$  and length  $L_g$ . The corresponding drain, source electrodes, and gate insulator layer are positioned underneath the gate arrays. The channel region has width  $W_{ch}$  and length  $L_{ch}$  and lies between the drain and the source electrode. In the initial state, the gate covers half of the channel width, as shown in Fig. 7(c).

When a lateral force  $F_Y$  is applied at the probe, the beams are involved in bending deformation. The gate arrays in the center mass move laterally and change the width of the channel area, which is expressed as follows:

$$W_{F_Y} = \frac{F_Y L_b^3}{48EI_V} \tag{14}$$

**Fig. 6.** Relationship between the saturated channel currents  $I_{dsc}$  and  $I_{dsu}$ , and the electrical parameters and geometry parameters at different width positions. (a) Net concentration of ionized acceptors in the substrate  $N_a$  with effective channel charge density  $Q'_{eff}$ ; (b) channel length  $L_{ch}$  and air gap  $Z_{air}$ .  $L_{ch}$  is 5 μm and  $Z_{air}$  is 0.25 μm for (a), and  $Q'_{eff}$  is 2.5 × 10<sup>-8</sup> C·cm<sup>-2</sup> and  $N_a$  is 1 × 10<sup>15</sup> cm<sup>-3</sup> for (b).

Fig. 7. Schematics of the proposed LMGFET force sensor. (a) Movable structure design; (b) movable sandwich structure containing a gold gate array layer and two photoresistive SU-8 layers; (c) arrangement and dimension of the movable gate arrays. The coordinate axis direction in all 3D models is based on the principle that the positive direction of the Z-axis is from the upper movable structure to the substrate, the positive direction of the Y-axis is from the sensor probe to the end of the movable structure, and the positive direction of the X-axis is from the left side to the right side of the sensor. S1, S2: two series of gold gate arrays; Line\_1, Line\_2: lateral lines;  $W_g$ : gate width;  $L_g$ : gate length;  $D_{off}$ : offset distance.

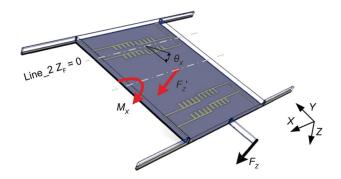

Young's modulus of the structural materials;  $I_Y = \frac{W_b T_b^3}{12}$  is the moment inertia of the beam vertical section; and  $L_b$ ,  $W_b$ , and  $T_b$  are the length, width, and thickness of the supporting beam, respectively. When a vertical force  $F_Z$  is applied, the structure experiences a vertical force applied at mass center  $F_Z'$  and a force-induced moment  $M_X = F_Z(L_p + \frac{1}{2}L_m)$  (where  $L_p$  is the probe length and  $L_m$  is the center mass length), which involve a vertical translation  $Z_F$  and a rotation around the X-axis for mass  $\theta_X$ , as shown in Fig. 8; their expressions are

$$Z_{\rm F} = \frac{F_Z L_{\rm b}^3}{48EI_Z} \tag{15}$$

$$\theta_{X} = \frac{M_{X}L_{b}^{3}}{24EI_{Z}(L_{m} - L_{b})}$$

(16)

where  $I_Z = \frac{T_{\rm b} W_{\rm b}^3}{12}$  is the moment inertia of the beam horizontal section. On this basis, a line with a distance of  $D_{\rm off}$  exists away from the mass center line and has zero vertical displacement. This line is expressed as follows:

$$D_{off} = \frac{L_m - L_b}{2L_p + L_m} \tag{17} \label{eq:defDoff}$$

The vertical displacement of the gate series from force  $F_Z$  is expressed as follows:

**Fig. 8.** Translation and rotation movements of a movable structure under vertical forces.  $Z_F$ ,  $\theta_X$ : vertical translation and rotation around the X-axis for mass, respectively.

$$Z_{F_Z} = \frac{F_z L_b^3}{48EI_z} \pm D \frac{M_X L_b^3}{24EI_z (L_m - L_b)}$$

(18)

where  $\pm D$  is the offset distance of the center lines between the gate array and mass, the minus sign before the D refers to the upper gate arrays in S2, and the plus sign refers to the downside gate arrays in S2. The deformation ratio between the lateral and vertical forces can be written as follows:

$$r = \frac{1}{\frac{T_b^2}{W_b^2} (1 \pm D \frac{2L_p + L_m}{L_m - L_b})}$$

(19)

A high r is achievable for structures whose thickness  $T_{\rm b}$  is larger than the width  $W_{\rm b}$ . Line\_2 should be set at this  $D_{\rm off}$  position, and the gate series S2 should be close to Line\_2 in order to decrease undesired vertical movement. The straight beams cannot suppress or stretch. Thus, the structure rarely deforms along an X-axis force  $F_X$ . Therefore, the proposed movable structure will only be sensitive to force along the Y-axis and will be free from interference from other directions.

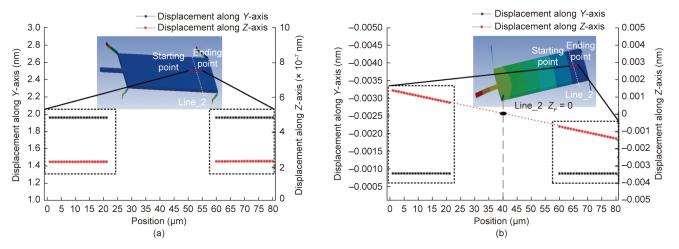

The proposed structure is simulated with ANSYS 15.0 to investigate its deformation behavior. The material and geometry parameters of the designed structure are given in Table 2. The geometry is modeled solely with an SU-8 structural layer, and the thin gold gate layer is ignored to reduce simulation complexity. In the simulations, the Young's modulus and Poisson's ratio of the SU-8 photoresist is 4.4 GPa [38] and 0.22 [39], respectively. The end of each beam is fixed, and a 1 nN force along the Y-/Z-axis is applied to the sidewall of the probe tip. Fig. 9 illustrates the deformation of gate series S2 under such forces. When a 1 nN lateral force is applied, the corresponding deformation is 1.961 nm, which is consistent with the theoretical value of 1.964 nm. Compared with the lateral movement under a Y-axis force, lateral movement caused by a Z-axis force is ignorable, as its value is approximately 0.00087 nm. The zero vertical deformation position  $D_{\rm off}$  is approximately 673 µm away from the mass center. The vertical deformation of the gate series S1 is approximately 0.001 nm. The

**Table 2**Material and geometry parameters of the designed structure.

| Parameters                              | Value   |

|-----------------------------------------|---------|

| Young's modulus of SU-8 photoresist     | 4.4 GPa |

| Poisson's ratio of SU-8 photoresist     | 0.22    |

| Thickness of lower SU-8 structure layer | 0.5 μm  |

| Thickness of upper SU-8 structure layer | 49.5 μm |

| Air gap $Z_{\rm air}$                   | 0.1 μm  |

| Length of center mass $L_{\rm m}$       | 2000 μm |

| Width of center mass $W_{\rm m}$        | 1700 μm |

| Length of gate $L_{ m g}$               | 20 μm   |

deformation ratio r is 1964, demonstrating the low cross-axis coupling effect in this structure.

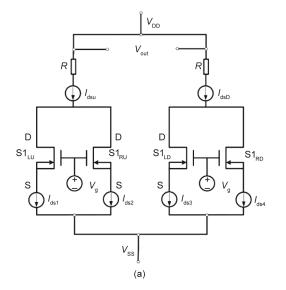

#### 3.2. Sensing configuration

Although the proposed structure rarely undergoes cross-axis deformation, undesired vertical deformation will inevitably bring interference to the channel current. Aside from the decoupling movable structure design, a sensing configuration is required to eliminate the cross-axis output coupling. A differential sensing configuration is normally adopted to compensate for loads from non-operation directions and for external disturbances, such as temperature and humidity. However, this method is unsuitable for LMGFET sensing because vertical movement of gate arrays different according to their position. In this research, a novel dualdifferential sensing configuration is proposed, in which the underlying channel region is not aligned with the gate arrays but is distributed anti-symmetrically about the center of Line\_1 and Line\_2, as shown in Fig. 10. Each transistor series is separated into four arrays:  $S1_{LU}$ ,  $S1_{LD}$ ,  $S1_{RU}$ , and  $S1_{RD}$  are for series S1, while  $S2_{LU}$ , S2<sub>LD</sub>, S2<sub>RU</sub>, and S2<sub>RD</sub> are for series S2. The interconnection configurations of S1 and S2 are illustrated in Figs. 11(a) and (b), respectively. S2 is for lateral force detection, and S1 is for vertical force detection. This paper focuses on lateral force detection. Thus, the following description is conducted with series S2.  $I_{dsL}$  is the sum of the current of two left transistor series  $S2_{LU}$  and  $S2_{LD}$ , and  $I_{dsR}$ is the sum of the current of two right transistor series  $S2_{RU}$ ,  $S2_{RD}$ . These expressions can be written as follows:

$$I_{dsL} = I_{ds1} (W_{chc} + W_{F_Y}, Z_{air} + Z_{F_Z}) + I_{ds2} (W_{chc} + W_{F_Y}, Z_{air} - Z_{F_Z})$$

(20)

$$I_{dsR} = I_{ds3} (W_{chc} + W_{F_Y}, Z_{air} + Z_{F_Z}) + I_{ds4} (W_{chc} + W_{F_Y}, Z_{air} - Z_{F_Z})$$

(21)

where  $I_{ds1}$ ,  $I_{ds2}$ ,  $I_{ds3}$ , and  $I_{ds4}$  are the current of the transistor series  $S2_{LU}$ ,  $S2_{LD}$ ,  $S2_{RU}$ ,  $S2_{RD}$ , respectively.

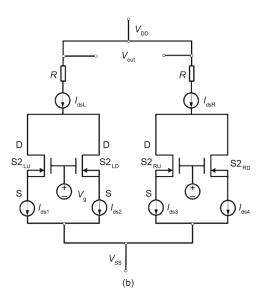

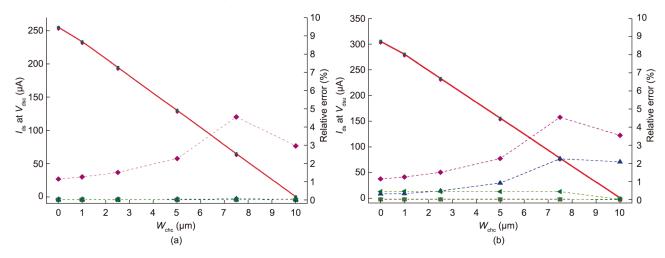

Most vertical interferences are counteracted in Eqs. (20) and (21). The final sensor output can be measured with the potential difference between two circuit branches,  $V_{\rm out} = R \times (I_{\rm dsL} - I_{\rm dsR})$  (where R is the connected resistor in the readout circuit). The sensing performance of the proposed dual-differential configuration is illustrated in Fig. 12 and is compared with the normal differential method, where the channel region is aligned with the gate array. The difference between the initial output and that under the vertical displacement is measured with relative errors for the two methods, as shown in Figs. 12(a) and (b).

For a 1 nN force loaded in the sensor probe, the sandwich structure moves 1.961 nm laterally but 0.001 nm vertically. Therefore, the vertical displacement is set from 0.001 to 3.000 nm in order to investigate the sensing performance under vertical forces ranging from 1 nN to 3  $\mu$ N. The relative errors of the two methods are negligible for a small vertical displacement of less than 0.03 nm. Because of the rapid increased  $C'_{\rm effu}$ , the relative error of the differential channel current increases until  $W_{\rm chc}$  reaches 7.5  $\mu m$ . The relative error of the normal differential method at  $V_{\rm dsc}$  reaches 4.53% for a 3 nm vertical displacement, and that of the proposed method is less than 0.01%. When  $W_{\rm chc}$  reaches 10  $\mu$ m, the relative errors solely resulting from the covered area exhibit a drop because  $C'_{\rm effu}$  disappears.  $V_{\rm dsu}$  has a higher change rate than  $V_{\rm dsc}$  because  $C_{\mathrm{effu}}'$  is more susceptible to air gap size than  $C_{\mathrm{effc}}'$ ; the relative errors at  $V_{dsu}$  show an increase compared with those at  $V_{dsc}$ , as shown in Fig. 12(b). The relative errors of the normal differential method at  $V_{\rm dsu}$  increase to 2.24% and 4.76% for vertical displacements of 0.03 and 3.00 nm, respectively, but the largest relative error of the proposed configuration remains as low as 0.43%. Considering the

Fig. 9. Deformation of the movable structure under a 1 nN force. (a) Deformation of the gate series S1 under a force along the Y-axis; (b) deformation of the gate series S1 under a force along the Z-axis.

**Fig. 10.** The proposed dual-differential sensing configuration,  $S1_{LU}$ ,  $S1_{LD}$ ,  $S1_{RU}$ , and  $S1_{RD}$  are transistor series for S1;  $S2_{LU}$ ,  $S2_{LD}$ ,  $S2_{RU}$ , and  $S2_{RD}$  are transistor series for S2.

deformation behavior of the movable structure, a 3 nm vertical deformation of the gate series S1 demands a vertical force of 3  $\mu$ N. The gate series cannot deform at 3 nm because the mass end face could touch the substrate under vertical forces below such a value. Therefore, the cross-axis coupling effect is thoroughly eliminated in the proposed dual-differential sensing configuration.

### 4. Model validation and sensor performance

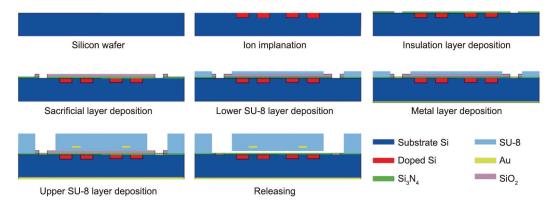

## 4.1. Fabrication process

A simple but practicable fabrication is proposed for the presented LMGFET device, as shown in Fig. 13. A photoresist layer is deposited and patterned to define the drain and source electrode and its interconnections; the substrate is then ion-implanted to form phosphorus-doped areas. Through another patterned photoresistive layer, the channel area is defined and then doped with phosphorus ions but using different implantation doses and

Fig. 11. Schematic of the proposed dual-differential configuration. (a) Interconnection of gate series S1; (b) interconnection of gate series S2. D: the common drain electrode; S: the common source electrode;  $V_{DD}$ : voltage applied at the common drain electrodes;  $V_{ss}$ : voltage applied at the common source electrode;  $V_{g}$ : voltage applied at the common gate electrodes. R: resistor;  $I_{dsD}$ : the sum of the current of two left transistor series  $S2_{LD}$  and  $S2_{RU}$ ;  $I_{dsD}$ : the sum of the current of two left transistor series  $S2_{LD}$  and  $S2_{RU}$ ;  $I_{dsD}$ : the sum of the current of two left transistor series  $S2_{LD}$  and  $S2_{RD}$ ;  $I_{dsD}$ : the sum of the current of two right transistor series  $S2_{RU}$ ,  $S2_{RD}$ ;  $I_{ds1}$ - $I_{ds4}$ : the current of the transistor series  $S2_{LD}$ ,  $S2_{LD}$ ,  $S2_{RD}$ ,  $S2_{RD}$ , respectively.

- Differential current under 0 nm vertical displacement Dual-differential current under 0 nm vertical displacement

- Differential current under 0.001 nm vertical displacement

- Dual-differential current under 0.001 nm vertical displacement

- Differential current under 0.03 nm vertical displacement

- Dual-differential current under 0.03 nm vertical displacement

- Differential current under 3 nm vertical displacement

- Dual-differential current under 3 nm vertical displacement

- -- -- Relative error of Differential current under 0.001 nm vertical displacement

- -- •-- Relative error of Dual-differential current under 0.001 nm vertical displacement

- -- A-- Relative error of Differential current under 0.03 nm vertical displacement

- --▼-- Relative error of Dual-differential current under 0.03 nm vertical displacement

- Relative error of Differential current under 3 nm vertical displacement

- Relative error of Dual-differential current under 3 nm vertical displacement

Fig. 12. Sensing performance of the proposed dual-differential configuration under different saturated voltages. (a) Channel current at saturated drain voltage  $V_{\rm dsc}$ ; (b) channel current at saturated drain voltage V<sub>dsu</sub>. Straight lines indicate the output current under 0 nm vertical displacement, scatters indicate the output under different vertical displacements, and dashed lines with scatters represent the relative output error of the two sensing configurations.

energies. The implanted ions are activated through rapid thermal annealing. A gate insulation layer made of silicon nitride is deposited and then patterned to expose contact holes for source/drain interconnections. Subsequently, a sacrificial layer of silicon dioxide is deposited and patterned to expose the structure anchors and contact holes. A thin SU-8 structural layer is spun, exposed, and developed to act as the lower layer of the sandwich structure. A gold layer is then deposited and patterned to act as the gate arrays and pads of the drain and source electrodes. The substrate metal pad is formed through another gold layer deposited on the bottom side of the chip. Another thick SU-8 layer is spun to seal the gate array and is patterned for the upper sandwich structural layer. The substrate is patterned with deep reactive ion etching to expose the probe area. Finally, isotropic etching of the sacrificial silicon dioxide layer is conducted to release the movable sandwich

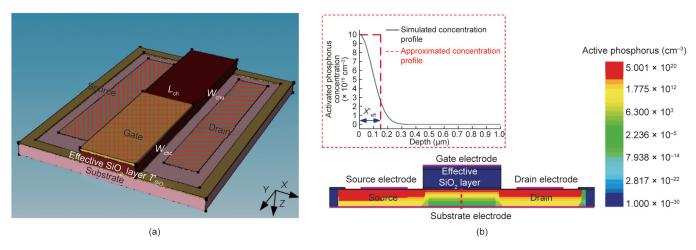

The fabrication process is simulated using FEM Software Sentaurus 13.0; the adopted parameters are illustrated in Table 3 and the simulated LMGFET unit is shown in Fig. 14(a). The device

Table 3 Parameters in fabrication simulation.

| Parameters                                                                                                                                                                                                                                                                                                      | Value                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Acceptor concentration of silicon substrate $N_{\rm a}$ Thickness of insulator silicon nitride $T_{\rm insu}$ Thickness of gold gate $T_{\rm g}$ Thickness of effective silicon dioxide $T_{\rm insu}$ Length of channel $L_{\rm ch}$ Width of channel $W_{\rm ch}$ Implanted depth of source/drain $X_{\rm j}$ | 1 × 10 <sup>15</sup> cm <sup>-3</sup><br>100 nm<br>0.2 μm<br>1 μm<br>5 μm<br>20 μm<br>0.5 μm |

| Implanted depth of channel                                                                                                                                                                                                                                                                                      | 0.15–0.30 μm                                                                                 |

is modeled as a single transistor to simplify the computation complexity, and the air gap and lower SU-8 structural layer are replaced with an effective silicon dioxide layer  $T_{\mathrm{SiO}_2}'$  by using the following expression:

$$T'_{\rm SiO_2} = \frac{\varepsilon_{\rm SiO_2} Z_{\rm air}}{\varepsilon_0} + \frac{\varepsilon_{\rm SiO_2} T_{\rm low\_SU-8}}{\varepsilon_{\rm SU-8}} \tag{22}$$

Fig. 13. Flow chart of the proposed fabrication process.

Fig. 14. Simulation of the proposed fabrication process. (a) 3D LMGFET unit in the simulation. (b) Implantation concentration in the simulated device; (upleft) extracted implantation ion profile along the dotted line in the channel area.  $X'_{\text{eff}}$ : the effective implantation depth.

where  $T_{\rm low\_SU-8}$  and  $\varepsilon_{\rm SU-8}$  are the thickness and permittivity of the lower SU-8 layer, and  $\varepsilon_{\rm SiO_2}$  is the permittivity of silicon dioxide. The peak implanted ion concentration in the channel area is  $1\times 10^{17}$  cm $^{-2}$ , which is achievable in the bath fabrication process as discussed in our previous work [25]. The characteristic of how the distribution of channel impurities influences the channel current is investigated by setting different ion implantation depths from 0.150 to 0.300  $\mu m$ . Fig. 14(b) shows a cross-section view of the activated implanted phosphorous distribution at an implantation depth of 0.275  $\mu m$ . The inset shows the extracted concentration profile of active phosphorus in the channel region for the device in Fig. 14(a). A rectangular approximation is modeled to describe the concentration profile, as shown by the read dot-

ted line in Fig. 14(b). The effective channel charge density  $Q_{\rm eff}'$  is set as the product of the peak phosphorus density and the effective implantation depth. Table 4 lists the derived electrical parameters at different implantation depths.

#### 4.2. Electrical model validation

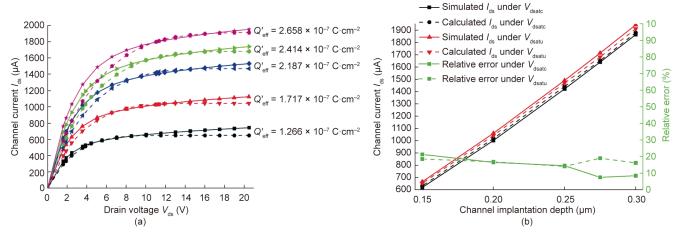

Four different electrodes are set in the gate, source, drain, and substrate region and modeled as red grids to investigate the electrical output behaviors, as shown in Fig. 14(a). A voltage of 0 is applied to the gate, source, and substrate electrodes, because the fabricated transistor is a depletion-type device. Fig. 15(a) shows the channel output current  $I_{\rm ds}$  characteristics under different chan-

Table 4

Extracted parameters under different implantation depths.

| Implantation depth (μm) | $X'_{\rm eff}$ ( $\mu m$ ) | Q′ <sub>eff</sub> (C⋅cm <sup>-2</sup> ) | $V_{\rm dsatc}$ (V) | $V_{\rm dsatu}$ (V) |

|-------------------------|----------------------------|-----------------------------------------|---------------------|---------------------|

| 0.150                   | 0.0791                     | $1.266 \times 10^{-7}$                  | 7.127               | 10.658              |

| 0.200                   | 0.1073                     | $1.717 \times 10^{-7}$                  | 9.585               | 13.767              |

| 0.250                   | 0.1367                     | $2.187 \times 10^{-7}$                  | 11.978              | 16.812              |

| 0.275                   | 0.1509                     | $2.414 \times 10^{-7}$                  | 13.094              | 18.234              |

| 0.300                   | 0.1661                     | $2.658 \times 10^{-7}$                  | 14.270              | 19.737              |

**Fig. 15.** Channel output current  $I_{ds}$  characteristics under different implantation depths. (a) Relationship between channel current  $I_{ds}$  and applied drain voltage  $V_{ds}$ ; (b) saturated channel current  $I_{ds}$  and the corresponding relative errors between the calculated and simulated results. Solid lines indicate the simulated channel current, while dotted lines indicate the calculated channel current.

nel implantation profiles when the applied drain voltage  $V_{

m ds}$ increases from 0 to 20.5 V. When the implantation depth is  $0.15~\mu m$ , the theoretical dotted line agrees well with the solid simulated line throughout the whole voltage range. The difference between the theoretical and simulated lines increases as the implantation depth increases. More specifically, the calculated current is smaller than that of the simulation for a low drain voltage, indicating that the proposed model is conservative in the nonsaturation region. This characteristic is associated with the errors from the implantation approximation. However, the saturation region exhibiting the maximum controllable measuring sensitivity is the focus of this research, in which the theoretical calculation and simulations are in excellent accordance for all implantation depths. The calculated channel current is compared with the simulated one at the saturated voltages  $V_{\rm dsc}$  and  $V_{\rm dsu}$ ; their relative errors are all less than 2% and are shown in Fig. 15(b).

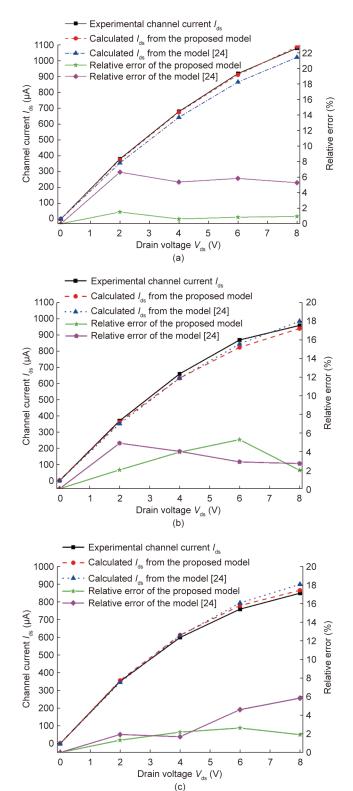

The theoretical model is validated using the experimental data from Ref. [24] and is compared with the literature-adopted model, which assumes a constant effective gate capacitance in the uncovered channel area  $C_{\mathrm{effu}}'$  and utilizes a regulation parameter for estimating the modulation effects. The experimental parameters extracted from Ref. [24] are listed in Table 5. In this study, the effective gate capacitance in the uncovered channel area  $C'_{effu}$  is constant and derived from the covered width  $W_{\rm chc}$  of 18  $\mu m$ . In fact,  $C_{\mathrm{effu}}'$  should increase with the increase in  $W_{\mathrm{chc}}$ , as discussed in Section 2. Fig. 16 provides a comparison of the calculated channel current from the proposed model and the model in Ref. [24]. The two models show similar accuracy for 18  $\mu$ m  $W_{chc}$ . The proposed model presents a close estimation for the outputs under the covered channel widths  $W_{\rm chc}$  of 0 and 60  $\mu m$ . The largest relative error of the proposed model is 1.51% for a  $W_{\rm chc}$  of 0 and 2.63% for a  $W_{\text{chc}}$  of 60  $\mu m$ . However, those of the improved model are 6.64% and 5.84%, respectively. Therefore, the proposed model is more accurate than the previous model for LMGFET performance analysis.

## 4.3. Discussion of sensor performance

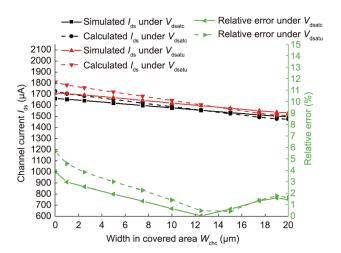

For sensor performance evaluation, the output channel current of the proposed sensor is obtained at different gate positions. Fig. 17 presents the saturated channel currents  $I_{\rm dsatc}$  and  $I_{\rm dsatu}$  of the simulations and calculation for an implantation depth of  $0.275 \, \mu m$ . The saturated voltages  $V_{dsatc}$  and  $V_{dsatu}$  are set to 10.2and 12.1 V, respectively, which are the lowest values during sensor operation. The relative error between the theoretical and simulated saturated currents is 3.88% and 5.64% at 0  $\mu m$   $W_{chc}$ . The mismatch under the condition of a small covered channel width mainly results from the estimation error of the capacitance expression (Eq. (2)). The relative error becomes less than 3.80% for  $W_{\rm chc}$  > 1  $\mu$ m. The sensitivity of the proposed device is 8.39 and 9.12  $\mu$ A·nN<sup>-1</sup> for the saturated voltages  $V_{dsatc}$  and  $V_{dsatu}$ , respectively. Due to the low stiffness of the SU-8 movable structure, the force sensitivity of the proposed LMGFET sensor is 4.65  $\mu$ A·nN<sup>-1</sup>, which is lower than that of our previous VMGFET device,

**Table 5**Experimental parameters of the fabricated LMGFET device [24].

| Parameters                                                       | Value                                                |

|------------------------------------------------------------------|------------------------------------------------------|

| Length of channel $L_{\rm ch}$                                   | 30 $\mu$ m                                           |

| Total channel width $W_{\rm ch} = W_{\rm chc} + W_{\rm chu}$     | 60 $\mu$ m                                           |

| Studied covered channel width $W_{\rm chc}$                      | 0, 18, 60 $\mu$ m                                    |

| Gate oxide thickness $T_{\rm insu}$                              | 27 nm                                                |

| Acceptors concentration of silicon substrate $N_{\rm a}$         | $1 \times 10^{15} \text{ cm}^{-3}$                   |

| Effective channel charge density $Q'_{\rm eff}$                  | $2.37 \times 10^{-7} \text{ C} \cdot \text{cm}^{-2}$ |

| Work function difference $\varphi_{\rm MS}$                      | -0.30  V                                             |

| Effective gate oxide capacitance in covered area $C'_{\rm effc}$ | $1.55 \times 10^{-8} \text{ F} \cdot \text{cm}^{-2}$ |

which had a value of  $12.53 \, \mu A \cdot n N^{-1}$  [25]. Nevertheless, it is much higher than those of previous VMGFET devices with values of 3.24 [22] and  $0.05 \, \mu A \cdot n N^{-1}$  [23], and higher than that of a reported LMGFET device with a value of  $0.01 \, \mu A \cdot n N^{-1}$  [24]. The nonlinearity experiences a slight fluctuation because the transistor in either the covered channel area or the uncovered area disappears when the

**Fig. 16.** Theoretical calculation and experimental measurement of channel current  $I_{\rm ds}$ . (a) Gate fully uncovers the channel area,  $W_{\rm chc}$  = 0  $\mu$ m; (b) gate partially covers the channel area,  $W_{\rm chc}$  = 18  $\mu$ m; (c) gate fully covers the channel area,  $W_{\rm chc}$  = 60  $\mu$ m.

**Fig. 17.** Theoretical calculation and experimental measurement of channel current  $I_{\rm ds}$  under different channel widths  $W_{\rm chc}$ .

channel is fully covered or exposed. The nonlinearity approaches 0.19% and 0.78% for a  $W_{chc}$  ranging from 2.5 to 17.5  $\mu$ m and from 1 to 19  $\mu$ m, respectively, which is much less than that of existing MGFET devices. The measurement range of the proposed sensor is  $\pm 5.10~\mu$ N, which is relatively less than that of the LMGFET device in Ref. [24] but much larger than those of VMGFET devices [22,23,25].

To evaluate the overall sensing performance, the product of the sensitivity, linearity, and measurement range is calculated as a merit factor, as shown in Table 6 [22–25]. The proposed sensor exhibits the largest merit factor of 47.07 mA among existing MGFET devices, indicating that a delicate tradeoff has been made between high sensing accuracy and a large measurement range for the proposed sensor. All these characteristics make the proposed sensor a suitable choice for the measurement of ultralow forces below the nano-newton level, especially for biomedical applications requiring a large measurement range, such as cell deformation squeezing and cellular membrane penetration.

# 5. Conclusions

In this paper, an LMGFET micro force sensor was proposed and comprehensively analyzed. The electrical behavior of the small LMGFET unit was theoretically modeled into two individual parts and tested with simulations and experimental data. The proposed sensor exhibited improved accuracy and capability for device performance evaluation before mass fabrication. A novel sandwich structure containing a gold gate array layer and two covered SU-8 photoresist layers was developed by decoupling multiple gate arrays and using a dual-differential sensing configuration. The output current under cross-axis loadings was considerably suppressed. The electrical and structural parameters of LMGFET devices were fully analyzed in order to optimize the sensor perfor-

mance, and a practicable fabrication process was developed and simulated. The proposed sensor exhibits considerably high sensitivity, linearity, and a large measurement range, making it a versatile sensing tool for biomedical micromanipulation tasks.

## Acknowledgments

This work is supported in part by the National Natural Science Foundation of China (52105589 and U1909221), in part by the China Postdoctoral Science Foundation (2021M692590), in part by the Beijing Advanced Innovation Center for Intelligent Robots and Systems (2019IRS08), in part by the Fundamental Research Funds for the Central Universities (China) (xzy012021009), and in part by the State Key Laboratory of Robotics and Systems (HIT) (SKLRS2021KF17).

# **Compliance with ethics guidelines**

Wendi Gao, Zhixia Qiao, Xiangguang Han, Xiaozhang Wang, Adnan Shakoor, Cunlang Liu, Dejiang Lu, Ping Yang, Libo Zhao, Yonglu Wang, Jiuhong Wang, Zhuangde Jiang, and Dong Sun declare that they have no conflict of interest or financial conflicts to disclose.

#### References

- [1] Dostanic M, Windt LM, Stein JM, van Meer BJ, Bellin M, Orlova V, et al. A miniaturized EHT platform for accurate measurements of tissue contractile properties. J Microelectromech Syst 2020;29(5):881–7.

- [2] Nakahara K, Sakuma S, Kawahara M, Takahashi M, Arai F. Time-lapse mechanical characterization of zona pellucida using a cell carrier chip. J Microelectromech Syst 2018;27(3):464–71.

- [3] Corbin EA, Adeniba OO, Ewoldt RH, Bashir R. Dynamic mechanical measurement of the viscoelasticity of single adherent cells. Appl Phys Lett 2016;108(9):093701.

- [4] Pu H, Chen H, Sun Yu, Liu Na, Yu J, Yang Y, et al. Micropipette aspiration of single cells for both mechanical and electrical characterization. IEEE Trans Biomed Eng 2019;66(11):3185–91.

- [5] Tsukagoshi T, Nguyen TV, Shoji KH, Takahashi H, Matsumoto K, Shimoyama I. Cellular dynamics of bovine aortic smooth muscle cells measured using MEMS force sensors. J Phys D Appl Phys 2018;51(14):145401.

- [6] Pan P, Qu J, Zhang W, Dong X, Wei W, Ru C, et al. Robotic stimulation of freely moving *Drosophila* larvae using a 3D-printed micro force sensor. IEEE Sens J 2019;19(8):3165–73.

- [7] Zhang W, Pan P, Wang X, Chen Y, Rao Y, Liu X. Force-controlled mechanical stimulation and single-neuron fluorescence imaging of *Drosophila* larvae. IEEE Robot Autom Lett 2021;6(2):3736–43.

- [8] Wei Y, Xu Q. Design and testing of a new force-sensing cell microinjector based on small-stiffness compliant mechanism. IEEE/ASME Trans Mechatron 2021;26(2):818–29.

- [9] Wei Y, Xu Q. A survey of force-assisted robotic cell microinjection technologies. IEEE Trans Autom Sci Eng 2019;16(2):931–45.

- [10] Cailliez J, Boudaoud M, Mohand-Ousaid A, Weill-Duflos A, Haliyo S, Régnier S. Modeling and experimental characterization of an active MEMS based force sensor. J Micro-Bio Robot 2019;15(1):53-64.

- [11] Qu J, Zhang W, Jung A, Silva-Da Cruz S, Liu X. Microscale compression and shear testing of soft materials using an MEMS microgripper with two-axis actuators and force sensors. IEEE Trans Autom Sci Eng 2017;14(2):834–43.

- [12] Grech D, Tarazona A, De Leon MT, Kiang KS, Zekonyte J, Wood RJK, et al. A quasi-concertina force-displacement MEMS probe for measuring biomechanical properties. Sens Actuators A Phys 2018;275:67–74.

Table 6

Performance comparison with existing MGFET devices.

|             | Sensitivity (μA·nN <sup>-1</sup> ) <sup>a</sup> | Nonlinearity (%) | Deformation range (μm) | Measurement range $(\mu N)$ | Merit factor (mA) |

|-------------|-------------------------------------------------|------------------|------------------------|-----------------------------|-------------------|

| This work   | 4.65                                            | 0.78             | ±10.0                  | ±5.10                       | 47.07             |

| LMGFET [24] | 0.01                                            | 7.28             | ±30.0                  | ±14.50                      | 0.32              |

| VMGFET [25] | 12.53                                           | 1.35             | 0.3                    | 0.42                        | 5.24              |

| VMGFET [22] | 3.24                                            | 11.12            | 0.2                    | 0.12                        | 0.35              |

| VMGFET [23] | 0.05                                            | 17.75            | 1.0                    | Na                          | Na                |

Na: not available.

<sup>&</sup>lt;sup>a</sup> Sensitivity is unified into the same unit.

- [13] Stavrov VT, Shulev AA, Hardalov CM, Todorov VM, Roussev IR. All-silicon microforce sensor for bio applications. In: Proceedings of SPIE

Microtechnologies; 2013 Apr 24–26; Grenoble, France. SPIE; 2013. p. 87630Y.

[14] Xie Y, Sun D, Liu C, Tse HY, Cheng SH. A force control approach to a robotassisted cell microinjection system. Int J Robot Res 2010;29(9):1222–32.

- [15] Xie Y, Zhou Y, Lin Y, Wang L, Xi W. Development of a microforce sensor and its array platform for robotic cell microinjection force measurement. Sensors 2016:16(4):483.

- [16] Gao W, Zhao L, Jiang Z, Xia Y, Guo X, Zhao Z, et al. A novel MEMS force sensor based on laterally movable gate array field effect transistor (LMGAFET). In: Proceedings of 2017 IEEE 12th International Conference on Nano/Micro Engineered and Molecular Systems (NEMS); 2017 Apr 9-12; Los Angeles, CA, USA, IEEE; 2017, p. 723-7

- [17] Zang Y, Zhang F, Huang D, Gao X, Di C, Zhu D. Flexible suspended gate organic thin-film transistors for ultra-sensitive pressure detection. Nat Commun 2015:6:6269

- [18] Ajmera PK, Song IH. Laterally movable gate FET (LMGFET) for on-chip integration of MEMS with electronics. In: Proceedings of SPIE's 8th Annual International Symposium on Smart Structures and Materials; 2001 Mar 4–8; Newport Beach, CA, USA. SPIE; 2001. p. 30–7.

- [19] Gao W, Shakoor A, Xie M, Chen S, Guan Z, Zhao L, et al. Precise automated intracellular delivery using a robotic cell microscope system with threedimensional image reconstruction information. IEEE/ASME Trans Mechatron 2020:25(6):2870-81.

- [20] Gao W, Shakoor A, Zhao L, Jiang Z, Sun D. 3D image reconstruction of biological organelles with a robot-aided microscopy system for intracellular surgery. IEEE Robot Autom Lett 2019;4(2):231-8.

- [21] Kang HS, Lee KH, Yang DY, You BH, Song IH, Micro-accelerometer based on vertically movable gate field effect transistor. Nano-Micro Lett 2015;7(3):

- [22] Aoyagi S, Suzuki M, Kogure J, Kong T, Taguchi R, Takahashi T, et al. Accelerometer using MOSFET with movable gate electrode: electroplating thick nickel proof mass on flexible Parylene beam for enhancing sensitivity. In: Proceedings of 2011 16th International Solid-State Sensors, Actuators and Microsystems Conference; 2011 Jun 5–9; Beijing, China. IEEE; 2011. p. 2030–3.

- [23] Coe DJ, English JM, Lindquist RG, Kaiser TJ. Model of a MEMS sensor using a common gate MOSFET differential amplifier. J Phys D Appl Phys 2006;39(20):

- [24] Song IH, Ajmera PK. A laterally movable gate field effect transistor. J Microelectromech Syst 2009;18(1):208-16.

- [25] Gao W, Jia C, Jiang Z, Zhou X, Zhao L, Sun D. The design and analysis of a novel micro force sensor based on depletion type movable gate field effect transistor. J Microelectromech Syst 2019;28(2):298-310.

- [26] Zhang A, Zhang L, Tang Z, Cheng X, Wang Y, Chen KJ, et al. Analytical modeling of capacitances for GaN HEMTs, including parasitic components. IEEE Trans Electron Dev 2014;61(3):755-61.

- [27] Bansal A, Paul BC, Roy K. An analytical fringe capacitance model for interconnects using conformal mapping. IEEE Trans Comput Des Integr Circuits Syst 2006;25(12):2765–74.

- [28] Bao M, Yang H, Yin H, Shen S. Effects of electrostatic forces generated by the driving signal on capacitive sensing devices. Sens Actuators A Phys 2000:84(3):213-9.

- [29] El-Mansy YA. Analysis and characterization of the depletion-mode IGFET. IEEE J Solid-State Circuits 1980;15(3):331-40.

- [30] Sun SC, Plummer JD. Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces. IEEE J Solid-State Circuits 1980;15(4): 562-73.

- [31] Arora N. MOSFET models for VLSI circuit simulation. Vienna: Springer Vienna; 1993

- [32] Coen RW, Muller RS. Velocity of surface carriers in inversion layers on silicon. Solid-State Electron 1980;23(1):35-40.

- [33] Ge C, Cretu E. A sacrificial-layer-free fabrication technology for MEMS transducer on flexible substrate. Sens Actuators A Phys 2019;286: 202 - 10.

- [34] Nagai M, Tanizaki K, Shibata T. Batch assembly of SU-8 movable components in channel under mild conditions for dynamic microsystems: application to biohybrid systems. J Microelectromech Syst 2019;28(3):419-28.

- [35] Ge C. Cretu E. Design and fabrication of SU-8 CMUT arrays through grayscale lithography. Sens Actuators A Phys 2018;280:368-75.

- [36] Vinje J, Beckwith KS, Sikorski P. Electron beam lithography fabrication of SU-8 polymer structures for cell studies. J Microelectromech Syst 2020;29 (2):160-9

- [37] Dai W, Lian K, Wang W. A quantitative study on the adhesion property of cured SU-8 on various metallic surfaces. Microsyst Technol 2005;11

- [38] Dai W, Lian K, Wang W. Design and fabrication of a SU-8 based electrostatic microactuator. Microsyst Technol 2007;13(3-4):271-7.

- [39] Microchem. Datasheet of SU-8 2025-2075 [Internet]. Newton: Microchem; 2009 Sep 22 [cited 2021 Sep 3]. Available from: https://kayakuam.com/ products/su-8-2000/.