Engineering 11 (2022) 18-20

Contents lists available at ScienceDirect

Engineering

journal homepage: www.elsevier.com/locate/eng

# Views & Comments Antenna-in-Package (AiP) Technology

Yueping Zhang

School of Electrical and Electronic Engineering, Nangyang Technological University, Singapore 639798, Singapore

# 1. Introduction

Since the mid-1990s, the complementary metal oxide semiconductor (CMOS) has been the technological driver for the wireless revolution [1], enabling the full system-on-chip (SoC) integration of Bluetooth radios, 60 GHz radios, and 79 GHz radar. In fact, the CMOS is now the dominant semiconductor technology for the fifth generation (5G) New Radio (NR) [2].

The antenna-in-package (AiP) concept was conceived to provide an advanced antenna solution for emerging wireless SoC or singlechip radio [3]. It explores packaging materials and processes to realize an antenna or array (or antennas or arrays) with a wireless chip (or chips) in a surface mount package. The AiP concept introduced for the first time the radiation function to the chip package. Consequently, it has enriched and upgraded the concept of a system in a package (SiP) [4,5]. Today, AiPs are the antenna and packaging technology for millimeter-wave (mmWave) 5G NR [6].

An antenna has a unique property of radiation, which makes wireless communication and detection possible. In a radio frequency (RF) band, it is a challenging task to reduce the antenna size while retaining radiation efficiency; in comparison, in an mmWave band, the difficulty lies in how to minimize the insertion loss of interconnects between the chip and array element. AiP technology provides an elegant solution to these challenges. Therefore, it has fundamentally changed the design and realization of radios and radar for wireless applications [7].

#### 2. Design considerations

The first change in radio and radar design was to motivate electronic design automation companies to develop codesign platforms to allow designers to implement design considerations for the seamless integration of antennas and chips in a package [8]. AiP technology creates new degrees of freedom to design both antennas and circuits: ① The constraint of a 50  $\Omega$  interface between an antenna and a circuit can be removed. The 50  $\Omega$  standard was optimized for a discrete antenna and circuit to be connected or measured with a coaxial cable. An AiP is an integrated structure in which traces, vias, and bumps are utilized for interconnects. ② A metal oxide semiconductor (MOS) transistor is the most important active device in an AiP. It acts as either a switch or a current source in a circuit. A transmit/receive switch is the circuit

that connects to the antenna. A novel codesign methodology of the antenna and switch with a full-wave electromagnetic solver such as high-frequency structure simulator (HFSS) has been developed, which treats the MOS transistor as an on-resistance or offcapacitance passive structure. This methodology is being extended for the codesign of the antenna and switch-based power amplifier. ③ If the MOS transistor needs to be modeled as a current source, the codesign must be conducted with a circuit simulator, such as Cadence AWR Microwave Office. The circuit simulator relies on compact models. Hence, the construction of a circuit model for an AiP is critical [9]. It has been shown that the circuit model can be physically derived or numerically extracted. ④ Inductors are commonly used to resonate with the parasitic capacitances of a MOS transistor. However, inductors are bulky and lossy, so it is preferable to avoid using them. Taking a low-noise amplifier with inductive source degeneration as an example, the traditional design uses two on-chip inductors, while the codesign can replace the inductors by exploring bond-wire inductance or making the antenna inductive (rather than 50  $\Omega$ ) in order to cancel the capacitive effect of the MOS transistors in the low-noise amplifier.

### 3. High-volume manufacturing (HVM) and testing

AiP technology has promoted the development of new materials and processes [10]. By new materials, I mean natural materials, not metamaterials. Nevertheless, over the last two decades, metamaterials have also aroused a great deal of research interest. A few AiP designs using metamaterials have also been attempted. It has been observed that using high-impedance surfaces as artificial magnetic conductors results in a thin profile and low backside radiation [11]. However, a metamaterial-based AiP is seldomly adopted by industries, probably because of the cost. HVM of AiPs started with a low-temperature co-fired ceramic (LTCC) material and process. A nonstandard process of either embedding an air cavity or piercing air holes in LTCC was developed to reduce surface waves and improve antenna radiation efficiency. Samsung and Intel respectively explored high-density interconnect (HDI) materials and processes for the mass production of AiPs for 60 GHz radios. International Business Machines Corporation (IBM) used organic materials and developed a surface laminar circuit (SLC) process for the HVM of large AiPs for mmWave 5G NR base stations [12]. Both the HDI and SLC mentioned above adopt

balanced substrates. A novel HDI process that realizes an unbalanced substrate was developed specifically for the low-cost fabrication of AiPs. The embedded wafer-level ball grid array (eWLB) technology, which was patented by Infineon, is radically different from LTCC, HDI, and SLC; eWLB features no laminate substrate, but has a copper redistribution layer [13]. It has proven to be an alternative approach for fabricating small AiPs in high volume [14]. However, a single redistribution layer limits the realization of a sophisticated AiP by means of eWLB. To obtain more redistribution layers, Taiwan Semiconductor Manufacturing Company (TSMC) developed the integrated fan-out (InFO), which routes the feeding network in the redistribution layer on the bottom side of the package, and the antenna elements in the redistribution layer on the top side. Thus, InFO-AiP can produce AiPs with a smaller form factor and higher gain for 5G NR terminals [15]. SJ Semiconductor Corporation (SISemi) developed the SmartAiP technology. which provides an ultra-high copper vertical interconnect, multilayer double-sided fine-pitch redistribution layers, wafer-level multi-layer precise aligned antennas, and more. The SmartAiP exhibits its low insertion loss advantage by offering a 24-43 GHz ultra-wideband solution to suit the various spectra allocated by different countries worldwide [16]. Moreover, a serious issue in AiPs is electromagnetic interference (EMI). A conformal shield and compartment shield using laser trenching, paste filling, and metal coating can suppress EMI effectively in an AiP.

AiP technology has advanced the measurement of antennas and packages to an unprecedented level. New testing methodologies and equipment are being developed and improved for AiPs. A probe-based antenna measurement setup has become necessary for the accurate characterization of AiPs in a laboratory [17]. Such a setup uses a ground-signal-ground (GSG) probe to feed the AiP and a standard gain born antenna rotating around the AiP at a far-field distance for radiation pattern measurement. Backside and bended probing techniques have been devised to minimize the effect of probe radiation, enhance the dynamic range, and reduce both the blockage and the interference due to reflections from a conventional probe. Fast testing of AiPs in a production line requires the use of automated test equipment (ATE) with an over-the-air (OTA) system [18]. An OTA system can be configured in the far, radiating-near, and reactive-near fields. It has been found that the radiating-near field holds significant advantages for high-volume production in terms of complexity and cost.

# 4. Applications

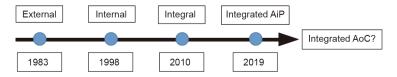

AiP technology has found many applications, including the Internet of Things at 2.4 GHz; virtual reality, augmented reality, and gesture recognition at 60 GHz; and automotive radars at 79 GHz. However, it is the application of AiP technology in 5G NR smart phones at 28 and 39 GHz that is truly groundbreaking. Fig. 1 shows the evolution of mobile phone antennas and a possible development trend. Regarding this figure, I must emphasize that integral and integrated antennas will coexist in smart phones, both now and in the future.

AiP technology will continue to find new applications; for example, the penetration of AiP technology into the medical field of noninvasive health monitoring is already underway. However, the entry barrier is high for medical applications because the product qualification cycles are far longer. The application of AiP technology to mmWave 5G-based industrial Internet has huge potential.

# 5. Conclusion

In summary, AiP technology is no longer an option; it is now mandatory for wireless SoCs. It will have a tremendous impact on both the antenna and the packaging industries. The traditional antenna industry will certainly lose some business, while outsourced semiconductor assembly and test (OSAT) companies will expand their business into the antenna domain for the first time. In the future, AiP technology will play an important role in realizing very large-scale antenna integration. It will also be used to enhance the terahertz antenna performance of antenna-on-chip technology [19].

#### References

- [1] Abidi AA. RF CMOS come of age. IEEE Microw Mag 2003;4(4):47-60.

- [2] Dunworth JD, Homayoun A, Ku BH, Ou YC, Chakraborty K, Liu G, et al. A 28GHz BULK-CMOS dual-polarization phased-array transceiver with 24 channels for 5G user and basestation equipment. In: Proceedings of 2018 IEEE International Solid-State Circuits Conference; 2018 Feb 11–15; San Francisco, CA, USA; 2018. p. 70–2.

- [3] Zhang YP. Antenna-in-package technology: its early development. IEEE Antennas Propag Mag 2019;61(3):111-8.

- [4] Liu D, Zhang YP. Integration of array antennas in chip package for 60-GHz radios. Proc IEEE 2012;100(7):2364–71.

- [5] Zhang YP, Sun M, Liu D, Lu Y. Dual grid array antennas in a thin-profile package for flip-chip interconnection to highly integrated 60-GHz radios. IEEE T Antenna Propag 2011;59(4):1191–9.

- [6] Elisabeth S, Malaquin C. Antenna in package (AiP): disrupting wireless communication and HMI. Chip Scale Rev 2020;24(1):4–7.

- [7] Rappaport TS, Heath RW, Daniels RC, Murdock JN. Millimeter wave wireless communication. New York: Pentice-Hall; 2015.

- [8] Issakov V, Wojnowski M, Knapp H, Trotta S, Forstner HP, Pressel K, et al. Cosimulation and co-design of chip-package-board interfaces in highlyintegrated RF systems. In: Proceedings of 2016 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM); 2016 Sep 25–27; New Brunswick, NJ, USA; 2016. p. 94–101.

- [9] Wang JJ, Zhang YP, Chua KM, Lu ACW. Circuit model of microstrip patch antenna on ceramic land grid array package for antenna-chip codesign of highly integrated RF transceivers. IEEE T Antenna Propag 2005;53(12): 3877-83.

- [10] Zhang YP, Mao JF. An overview of the development of antenna-in-package technology for highly integrated wireless devices. Proc IEEE 2019;107(11): 2265–80.

- [11] Kyriazidou CA, Contopanagos HF, Alexopoulos NG. Space-frequency projection of planar AMCs on integrated antennas for 60 GHz radios. IEEE T Antenna Propag 2012;60(4):1899–909.

- [12] Liu D, Gu X, Baks CW, Valdes-Garcia A. Antenna-in-package design considerations for Ka-band 5G communication applications. IEEE T Antenna Propag 2017;65(12):6372–9.

- [13] Brunnbauer M, Fürgut E, Beer G, Meyer T. Embedded wafer level ball grid array (eWLB). In: Proceedings of 2006 8th Electronics Packaging Technology Conference; 2006 Dec 6–8; Singapore; 2006.

- [14] Nasr I, Jungmaier R, Baheti A, Noppeney D, Bal JS, Wojnowski M, et al. A highly integrated 60 GHz 6-channel transceiver with antenna in package for smart sensing and short-range communications. IEEE J Solid St Circ 2016;51(9): 2066–76.

Fig. 1. The evolution of the setting of mobile phone antennas. AoC: antenna-on-chip.

### Y. Zhang

- [15] Tsai CH, Hsu CW, Kao KY, Tang TC, Lu CL, Wu KC, et al. Fabrication and characterization of millimeter wave 3D InFO dipole antenna array integrated with CMOS front-end circuits. In: Proceedings of 2019 IEEE International Electron Devices Meeting (IEDM); 2019 Dec 7–11; San Francisco, CA, USA; 2019.

- 2019.

[16] Yu B, Qian Z, Lin C, Lin J, Zhang YP, Yang G, et al. A wideband mmWave antenna in fan-out wafer level packaging with tall vertical interconnects for 5G wireless communication. IEEE T Antenna Propag 2021;69(10):6906–11.

- [17] Zheng Z, Zhang YP, Shi L, Wu L, Mao JF. An overview of probe-based millimetre-wave/terahertz far-field antenna measurement setups. IEEE Antennas Propag Mag 2021;63(2):63–118.

- [18] Moreira J. Testing AiP modules in high-volume production for 5G applications. Chip Scale Rev 2020;24(6):31–6.

- [19] Zhang YP, Liu D. Antenna-on-chip and antenna-in-package solutions to highly integrated millimeter-wave devices for wireless communications. IEEE T Antenna Propag 2009;57(10):2830–41.