《1 前言》

1 前言

大规模集成电路发展到深亚微米时代以后,技术的进步和特征尺寸的缩小导致互连线横截面和线间距减小、互连线密度以及互连引线层数增加,互连线的寄生耦合效应将会严重影响电路性能,其中互连时延已成为决定集成电路传输性能、可靠性等方面的关键因素之一。目前,随着 VLSI 芯片加工工艺的发展,互连时延已经超过门时延成为电路时延的主要部分,因此大规模集成电路的设计与分析必须考虑互连时延的影响,提出准确、高效、简洁的互连线时延估计模型具有重要意义。

长久以来 Elmore 时延模型[1]一直是进行互连线时延估计的主流模型。该模型是输入理想阶跃信号的一阶 RC 时延估计,但随着互连线特征尺寸的减小,电感耦合所导致的互连时延使互连问题更趋严重,此时仅通过 Elmore 模型进行时延估计会产生较大误差[2]。因此进行互连线时延估计时电感的作用不能忽略,目前已有学者提出了基于 RLC 互连线的等效 Elmore 时延模型[2,3]。

但以上时延估计模型的前提均为输入信号是理想阶跃信号,而实际电路中信号总有一定的上升或下降时间,此时以上时延模型就会产生较大误差。文献[4]提出了斜阶跃信号激励下时延模型的概念,不足之处在于所得模型较为复杂,且仅用于单根互连线,而没有考虑互连线的寄生耦合效应。针对耦合 RLC互连线进行分析,将斜阶跃信号激励下的耦合互连线模型在线元分析阶段进行解耦,结合二阶矩模型及改进的一阶模型[5]对互连线的传递函数进行化简,进而给出简洁的耦合互连线时延估计表达式。实验结果与 PSPICE 时延仿真比较,误差保持在 5 % 以内,表明文章提出的互连线时延估计方法可以对耦合 RLC 互连线模型的时延进行有效评估。

《2 斜阶跃激励下耦合互连线时延分析》

2 斜阶跃激励下耦合互连线时延分析

《2.1 耦合 RLC 互连线模型》

2.1 耦合 RLC 互连线模型

对 CMOS 电路器件进行线性假设,即驱动器端有驱动电阻,负载端有负载电容。将互连线分为相当数量的互连线元,并对每段线元使用混 π 模型,随着线元数趋于无穷,即可利用集总参数模型得到分布参数理论。

耦合互连线的 RLC 集总模型如图 1 所示,1 为攻击线,2 为受害线。其中,I 为激励信号 Vs 和驱动电阻 Rs ;II 为互连线的等效集总电路部分;由 n 个线元构成;III 为负载电容 Cl ;cc 为单位长度耦合电容;cg 为单位长度接地电容;r 为单位长度电阻;l 为单位长度电感;lm 为单位长度互感;dx =h/n 为每个线元的长度;h 为互连线长。

《图1》

图1 耦合 RLC 互连线集总模型

Fig.1 Coupled RLC interconnects lump model

《2.2 耦合 RLC 互连线模型解耦》

2.2 耦合 RLC 互连线模型解耦

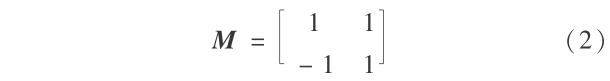

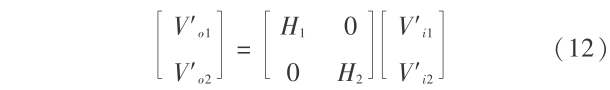

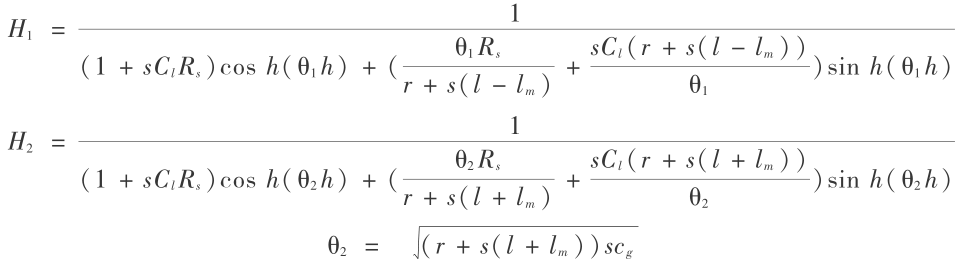

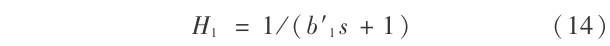

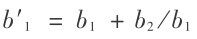

现取图 1 中 II 部分任意一段线元进行研究,令Vi1 ,Ii1 ,Vo1 ,Io1 分别为攻击线的近端电压电流和远端电压电流,Vi2 ,Ii2 ,Vo2 ,Io2 为受害线的近端电压电流和远端电压电流。根据基尔霍夫定律可得该线元复频域的系统方程[6]:

其中,

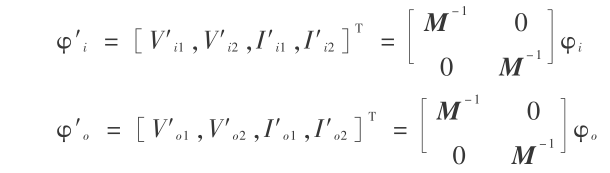

为对耦合线进行解耦[7,8],引入变换矩阵 M:

利用 M 进行变换可得解耦后线元的复频域系统方程:

其中,

以 φ′i 为输入, φ′o 为输出建立新的线元系统如图 2 所示,此时原本耦合的线元解耦为两条独立的互连线元。

《图2》

图2 解耦后的 RLC 线元模型

Fig.2 Decoupling RLC segment model

此时取图 2 线元系统的攻击线 1 进行分析,其传输矩阵为

引入变换矩阵 D,通过对角变换使传输矩阵E1′ 对角化为矩阵 F:

其中, 。

。

对其余 n -1 个线元进行同样的解耦操作,并将各段线元级联,此时整个耦合 RLC 互连线集总电路部分解耦为两条独立的互连线,各段线元级联后攻击线 II 部分的传输矩阵为

为对式(7)进行化简引入式(8),化简后可得式(9)方程。

考虑攻击线的边界条件[9],分别得图 1 中攻击线 I,III 部分的传输矩阵:

将式(9),(10),(11)级联即得解耦后 RLC 互连线集总模型的攻击线传输矩阵,其复频域系统方程为

其中,

将传递函数 H1 在 s = 0 处展开并取二阶多项式,此时 H1 可化简为如下形式:

其中,

在此引入改进的一阶模型[5] 对传递函数 H1 再次进行化简:

其中, 。

。

同理对 H2 进行同样操作可得

以上模型形式虽然是一阶的,但其精度却接近于二阶模型,可以达到精度与运算成本很好的折中。

《2.3 斜阶跃信号激励下的时延估计》

2.3 斜阶跃信号激励下的时延估计

实际电路中激励信号不可能是完全理想的,信号的上升和下降均不可能瞬间完成,而总有一定的上升和下降时间。此时若采用理想阶跃信号作为激励所得的时延模型就会产生误差,故文章采用斜阶跃信号作为激励信号对互连线进行时延分析。

《图3》

图3 斜阶跃信号的等效

Fig.3 The equivalent of ramp input

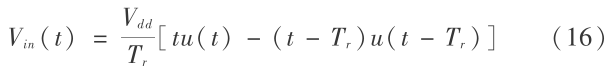

有限上升沿的斜阶跃信号可以等效为如图 3 所示的两个无限斜坡信号的累加,其中一个为上升沿信号,另一个为下降沿信号。其对应的时域表达式为

其中,Vdd 为激励信号幅值,Tr 为信号上升时间,u(t)为理想阶跃信号。

对式(16)进行拉普拉斯逆变换可得其复频域表达式:

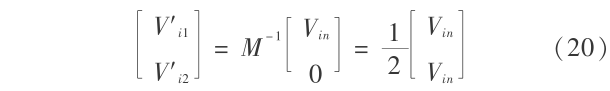

由式(3)知解耦前后电压关系满足:

根据式(18)可得解耦后 RLC 互连线集总模型的激励电压为

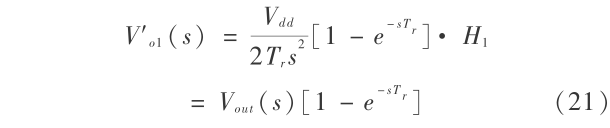

取解耦后的攻击线 1 进行分析,其复频域输出信号为

此时在激励为有限上升时间阶跃信号的情况下,输出信号的时域表达式为

同理可得解耦后受害线的输出信号时域表达式为

根据式(19)可得解耦前互连线的输出信号为

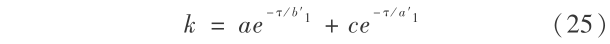

假设输出信号为 Vth ,对应的时延为  ,则可得关于

,则可得关于  的指数方程:

的指数方程:

其中,

考虑到式(25)为超越方程而无法直接得到解析解,故采用二分法求其数值解,从而得到互连时延  。

。

《3 RLC 互连模型实验结果与比较》

3 RLC 互连模型实验结果与比较

实验模型的激励信号均为斜阶跃信号,其幅值为 1 V,上升沿时间为 300 ps。

表 1 给出了选取的实验模型参数,利用上述的时延估计方法对其在 90 % 时延 (T0.9 ) 的情况下进行实验,并和 PSPICE 电路 CAD 软件的仿真结果进行比较。表 2 则给出了不同驱动电阻和负载电容下估计方法求得的互连时延,并与 PSPICE 仿真所得时延进行比较,进而得到相对误差来验证该方法在耦合互连线时延估计中的有效性。

《表1》

表1 RLC 集总模型参数

Table 1 The parameters of RLC lump model

《表2》

表2 互连时延相对误差

Table 2 The values and error of delay

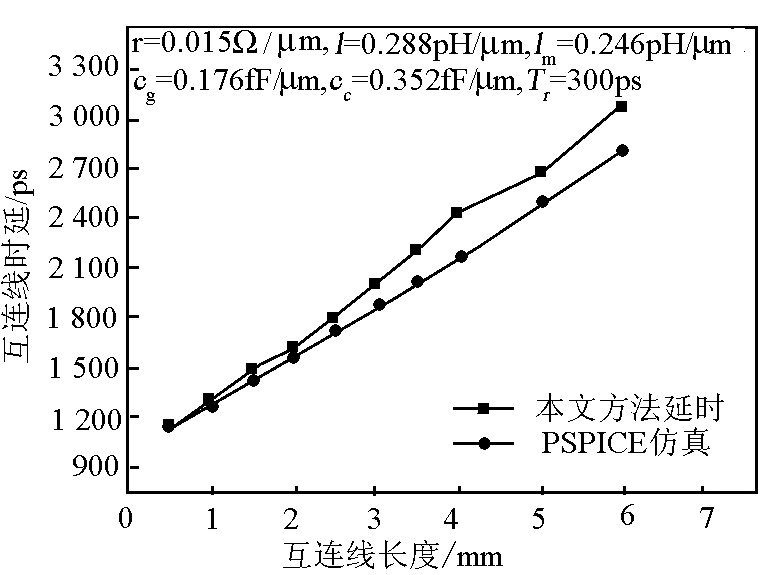

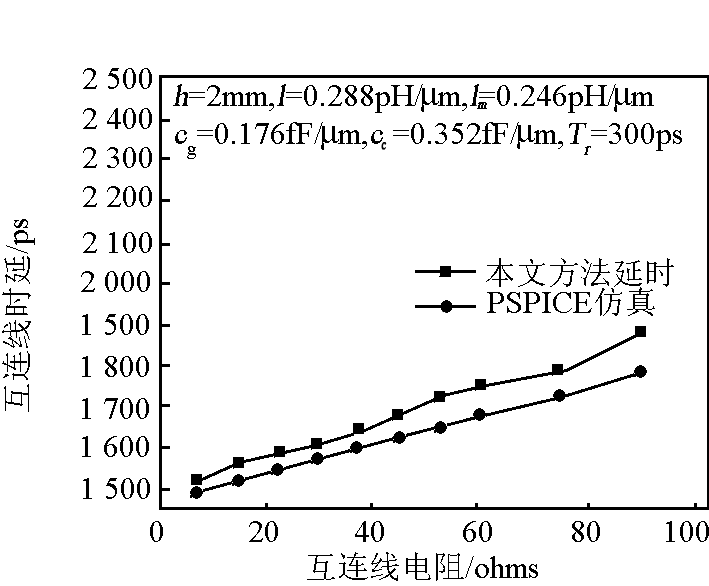

图 4 到图 7 分别给出了不同分布参数变化下估计方法与 PSPICE 仿真所得互连时延的比较曲线,可看出文中方法与 PSPICE 仿真结果吻合的较好,说明文中的时延估计方法可以准确地估计耦合互连线的时延。

《图4》

图4 不同线长下时延比较曲线

Fig.4 Delay of different interconnect length

《图5》

图5 不同线阻下时延比较曲线

Fig.5 Delay of different resistances

《图6》

图6 不同耦合电容下时延比较曲线

Fig.6 Delay of different coupling capacirances

《图7》

图7 不同上升时间下时延比较曲线

Fig.7 Delay of different rise time

以笔者估计方法所得时延结果与 PSPICE 结果进行比较,可以看出该方法所得结果均能较好地符合实验模型的仿真结果,具有较高的可靠性。

《4 结语》

4 结语

随着 VLSI 制造工艺进入深亚微米和超深亚微米阶段,互连时延对电压畸变及信号完整性等方面的影响正受到人们越来越多的关注。笔者考虑实际电路中激励信号不理想对耦合互连线时延分析的影响,建立了斜阶跃信号激励下的互连线时延模型。在线元分析过程中将原本复杂的耦合线元化简为独立线元,进而结合二阶矩模型及改进的一阶模型对互连线的传递函数进行化简,并以此对耦合互连线模型进行分析,给出了斜阶跃激励下互连时延的时域表达式。最后将实验结果与 PSPICE 仿真结果进行比较,验证了该方法在互连时延分析中的有效性。

京公网安备 11010502051620号

京公网安备 11010502051620号