《1 引言》

1 引言

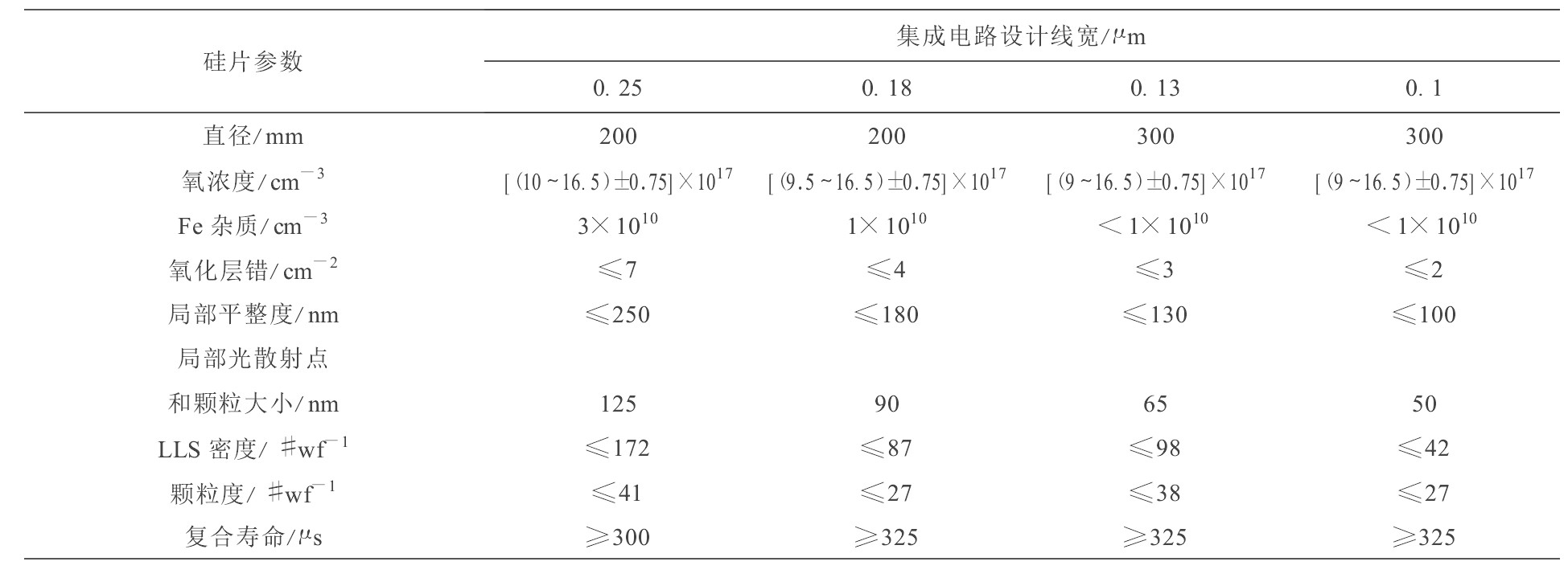

半导体硅作为现代电子工业的基础材料已有半个世纪的历史, 尽管集成电路密度遵循“摩尔定律”不断提高, 设计线宽急剧减小, 硅材料总能适应器件发展, 满足其越来越苛刻的要求。近年来, 世界各发达国家相继推出信息技术和知识经济方面的计划, 进一步奠定了半导体硅在21世纪持续发展的基础。可以预计, 大直径硅单晶片和硅基材料的均匀性、完整性及表面质量将成为决定新一代集成电路性能、成品率和可靠性的重要因素。图1所示为CMOS集成电路从1μm向0.1μm工艺过渡时, 其阈值电压、栅氧化层厚度对沟道宽度的变化[1]。表1为1998年半导体工业协会 (SIA) 公布的与亚四分之一微米级集成电路发展相适应的硅衬底片部分参数指标[2]。

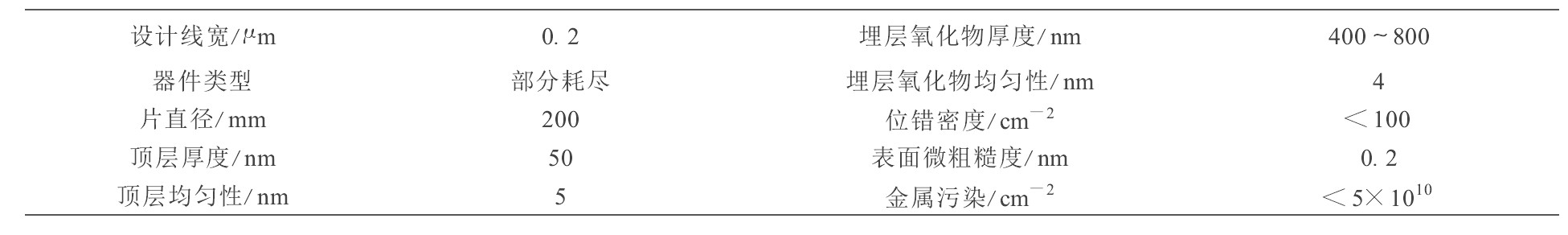

《表1》

表1 亚四分之一微米级集成电路所需硅材料的部分参数指标

Table 1 Starting silicon material requirements for sub-quarter-micron IC

图1 1~0.1μm CMOS工艺集成电路各主要参数变化

Fig.1 Electronic parameters and gate oxide thickness trends vs.channel length for CMOS technologies from 1~0.1μm

对于深亚微米和亚四分之一微米的超大规模集成电路所需的直径200 mm、300 mm乃至更大直径的硅片来说, 其成本、基本参数指标、金属污染、缺陷控制、表面形态等都面临着新的挑战。同时, 硅材料的标准、生产工艺、检测方法与技术也将成为今后研究的主要内容和推动产业发展的关键。此外, 硅基材料的研究与开发已日臻成熟, 并在器件与电路的制备方面取得了引人注目的成绩。本文还将介绍集成电路用外延硅、锗硅及SOI等硅基材料的特性、制备工艺技术以及跨世纪期间的发展前景。

《2 大直径硅单晶的研究进展》

2 大直径硅单晶的研究进展

进入超大规模集成电路时代以来, 大直径硅单晶一直是热门的研发课题。目前国际上主流工业产品为直径150 mm (6英寸) 和200 mm (8英寸) 硅片, ≥300 mm (12英寸) 硅材料仍处于研究阶段。我国已于1997年拉制出直径300 mm, 等径长度400 mm, 质量81 kg的硅单晶。国际半导体材料与设备协会也制定了直径300 mm的硅片标准。但是生长直径300 mm或大于300 mm的直拉硅单晶仍面临四个方面的问题:流体动力学的复杂性增强;传统的细颈不能支撑质量300 kg以上的晶棒;点缺陷影响明显, 消除氧化层错等缺陷更加困难;每次拉晶成本大大增加这意味着必须加强计算机模拟工作, 减少实验次数。Dupret等人[3]和Seidl等人[4]报告了生长大直径单晶熔体动力学数学模型, 比较了两种涡流模型的结果, 并发现熔体划分为三个对流区, 在中心区域熔体流动发生从“软”到“硬”涡流的变化。Chandrasekhar等人[5]和Tu等人[6]报告了以10 mm和6 mm、7 mm的缩颈技术生长直径300 mm无位错硅单晶的工艺, 发现粗籽晶无位错技术遵循Yip-Wilox[7]规律。屠海令等人[8]和Watanabe等人[9]报道了cusp磁场的轴向零磁面在熔体自由表面以下可实现稳定单晶生长, 并可生长出无条纹的晶体。为了减少直径大于300mm硅单晶巨额研究经费的负担, 日本于1996年成立了超级硅晶体研究所 (简称SSI) , 实行了5年计划, 包括直径400 mm的单晶制备、晶片加工和外延生长等三部分内容, 研究经费为1340亿日元。SSI采用德国Leybold公司的单晶炉, 882 mm (36英寸) 坩埚, 装料550 kg。直径400 mm的硅材料的研究刚刚开始, 而SIA则提出硅单晶由直径300 mm直接过渡到450 mm比较合理。有关这方面较详细的论述, 我们将另有专文向读者介绍。总之, 这一类的探索性研究还有待国际上多个材料与器件厂家合作, 才会有比较切实的进展和明朗的前景。

《3 点缺陷及其衍生缺陷的行为与晶体生长工艺》

3 点缺陷及其衍生缺陷的行为与晶体生长工艺

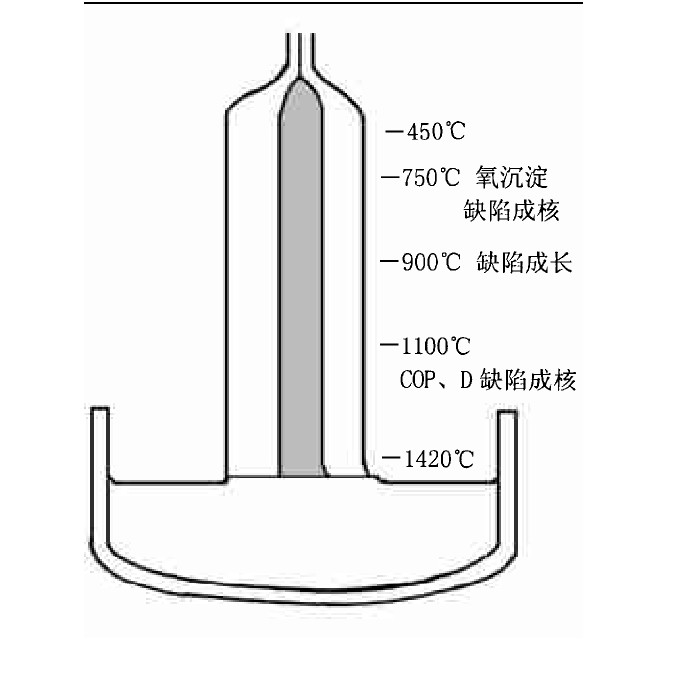

半导体硅材料中的缺陷一直是重要的研究课题。早在70年代中期, Rozgonyi[10]就提出了“wheel of misfortune”的概念, 并指出检测诊断技术及确定各种硅中缺陷具有举足轻重的作用。当时集成电路的工艺仅有50多步。现在, 随着集成电路密度向千兆位比特发展, 设计线宽趋于深亚微米、亚四分之一微米乃至纳米数量级, 制造工艺已超过400步, 成品率也大大提高, 因此硅单晶中点缺陷的作用愈来愈显得重要。硅中点缺陷由空位和自间隙原子组成, 其类型、浓度与分布, 直接和晶体生长工艺与热处理条件有关。1989年Hasebe[11]等人第一次报告当降低晶体拉速时, 氧化层错环 (OSF环) 从晶体边缘缩小到中心后消失。而后研究人员[12~15]发现几种长入缺陷, 如LSTD (laser scattering tomography defect) , FPD (flow pattern defect) , SEPD (secco etch pit defect) , COP (crystaloriginated pit) 等均由同一种八面体空洞构成, 这些八面体空洞是由晶体生长过程中的空位聚集而成。在晶体生长过程中, 有大量的上述长入缺陷, 密度约在106 cm-3左右。这些长入缺陷的形成过程大体包括两个阶段:首先在1100℃以下约30℃左右的狭窄温度范围内迅速形成空调;然后在1100℃到900℃的冷却阶段, 在空洞内壁形成氧化膜[16] (图2) 。大量实验数据表明, 大直径切克劳斯基直拉硅单晶的生长速度与固液交界面处的温度梯度是影响点缺陷的两个重要因素。理论计算也指出, 晶体生长速率V与点缺陷的输运相联系, 而晶体/熔体交界处的轴向温度梯度G与点缺陷在固液交界面的湮灭过程有关。V/G值的大小将决定晶体中点缺陷的类型和浓度[17]。Voronkov[18]提出V/G有一个经验临界值, 大约为1.3×10-3 cm-2m-1K-1, 大于此值, 则单晶中点缺陷以空位占优势。这种晶体在以后的加工过程中更易控制氧的沉积和衍生缺陷的密度。目前, 市场上销售的大直径硅单晶片多属此类, 其中含有空位聚集而形成的D缺陷[19], 这种缺陷与前面叙述的长入缺陷基本上属同一类型, 如不进行控制, 则影响器件性能与成品率。

图2 硅单晶生长过程中缺陷与氧沉淀成核生长的临界温区

Fig.2 Critical temperature ranges for defect agglomeration and oxygen precipitation during crystal growth

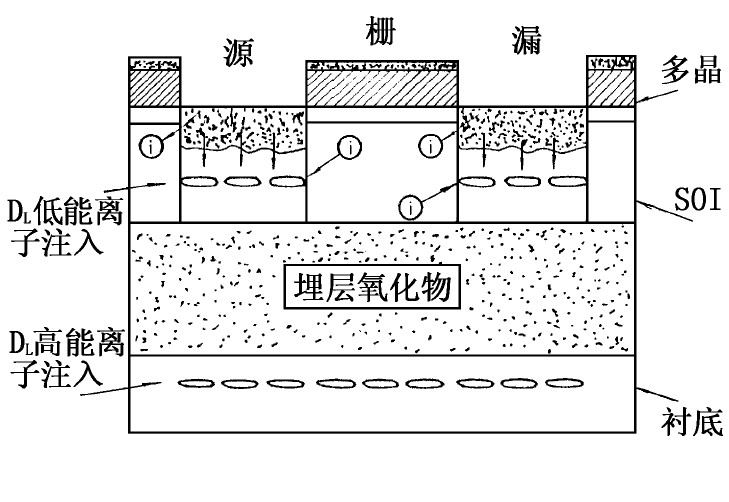

点缺陷动力学的计算机模拟仍处于发展的初期[20], 部分原因是需要热场和液流的模拟结果作为缺陷模拟的基础。单晶的热场和晶体/熔体界面形状的数学描述尤为重要。当模拟晶体生长中点缺陷动力学时, 通常以连续平衡模型为基础, 并考虑硅晶格内发生的扩散对流和反应过程在实际的硅单晶中, 缺陷的状态更为复杂, 因为空位和自间隙原子还要与氧原子结合, 形成复合体 (下面论述硅中氧与氧沉淀时再做进一步讨论) 。目前缺陷动力学模型, 可以定量地解释直拉单晶生长时点缺陷的三维分布、复合及二次缺陷 (有氧或无氧的存在) 的形成过程。事实上, 如何有效地控制和利用这些缺陷, 一直是半导体材料及器件工艺技术研究中的重要课题。从80年代提出缺陷工程的概念以来, 已有大量的研究成果并应用于改善硅片的质量和提高材料表面的完整性。其中内外吸除技术已广泛用于硅片和集成电路的制备工艺。缺陷工程的基本思路是控制并利用晶体生长和加工中产生的缺陷, 保证和提高材料与集成电路的性能, 缺陷工程的实施必须与材料的性能参数及集成电路工艺相匹配, 例如对低于1000℃的集成电路工艺来说, 硅片氧含量的选择既要权衡硅片翘曲的后果, 又要考虑保证内吸除机制。近年来, 外吸除工艺亦有新进展, 如沉积多晶硅、背面软损伤等, 它不仅适用于低氧含量硅片, 而且可与内吸除工艺配合产生更好的作用。对于SOI的多层结构, 传统的内外吸除方法不能奏效, 人们即采用离子注入法引进损伤, 然后进行横向吸除, 以改善源、漏区的质量 (图3) [21]。此外, 深亚微米级集成电路栅极二氧化硅层的漏电是影响电路质量和成品率的决定性因素, 栅氧化层完整性 (GOI) 的概念已被广泛采用, 以评价硅材料的质量。可以预计, 随着硅材料产业的发展, 硅中缺陷的行为与控制, 缺陷与杂质的互作用, 利用缺陷改善材料的质量, 以及拉制完美单晶和制备有“魔净区”的衬底片[22], 不仅是重要的研究课题, 而且具有广阔的应用前景。

图3 在SOI材料中采用离子注入横向吸除的缺陷工程示意图

Fig.3 Getting in SOI materials by ion-implantation defect engineering

《4 金属杂质行为与材料电学特性》

4 金属杂质行为与材料电学特性

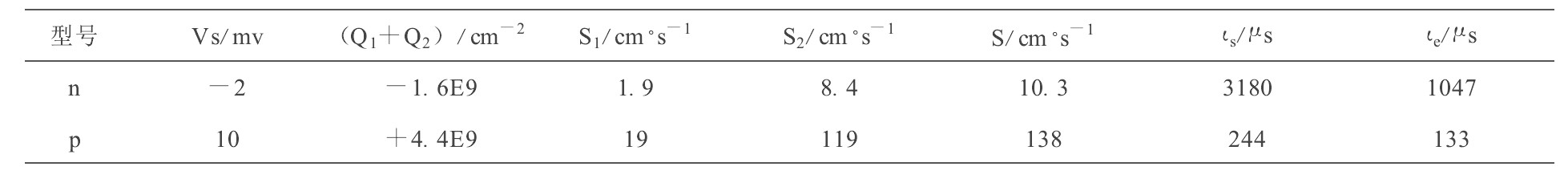

硅中金属特别是过渡金属杂质具有很高的电活性, 不仅能在p-n结和Si/SiO2界面处形成有害沉淀, 还会增强衬底表面的微粗糙度。目前, Cu、Fe是半导体硅工业中危害较大的两个金属元素。对于超大规模集成电路用硅片, 一般要求表面的Fe、Cu、Ni、Zn和Cr每种元素含量少于1011cm-2。目前大多数国外厂商都可满足上述要求, 并提供在30×30 mm2区域内的全反射X射线荧光谱 (TXRF) 数据。直径200 mm硅片表面金属含量指标已接近目前检测设备的灵敏度极限。表面浓度低于1010cm-2的测量技术主要采用气相分解 (VPD) 、原子吸收、ICP质谱与TXRF谱。为避免不可控的漏电流弱化DRAM电路的再生性能, 少子寿命扫描测量越来越派上用场。少子寿命测量是多个杂质元素综合量化结果, 要想提高兆位和千兆位集成电路的成品率, 必须在线控制Fe, Ni和Cu的污染并将其限制在1010~1011cm-2的范围。硅中少数载流子寿命主要取决于外来杂质和起陷阱作用的晶体缺陷, 因此硅片少子寿命的无损测量是研究的主要课题。近年来, 表面光电压法 (SPV) [23]测量硅中少子寿命取得了较大进展, 证实了氧沉淀与少子寿命衰减间的关系。Shimura[24]等人还研究了Na、Ni、Cu、W、Au、Cr、Co、Al、Fe对硅中少子寿命的影响。此外, 硅中间隙Fe与FeB复合体对表面复合速度和复合寿命的影响已成为大规模集成电路和硅材料电学性能研究中的热门课题[25]。屠海令等人[26]研究了工艺参数与p型硅片中铁浓度及其二维分布的关系并计算了对硅中少子扩散长度的影响。表2比较了p型与n型硅中的理论计算结果, 其中, Vs为表面势, Q1为SiO2中固定电荷, Q2为表面电荷, S1为SiO2/Si界面的复合速度, S2为铁污染硅的表面复合速度, S为表面复合速度, ιs为表面少子寿命, ιe为有效少子寿命。

《表2》

表2 p型与n型硅中表面势电荷复合速度与寿命

Table 2 Surface potentials, carriers, combination velocities and lifetimes for p type and n type silicon wafers

铜在硅中有较高的溶解度和扩散系数, 可在较低的温度下快速扩散, 多年来一直是半导体材料与器件制备工艺中极力避免的金属杂质。IBM宣布其铜导线技术开发成功后, 引起了集成电路制造业的极大兴趣。众所周知, 在亚四分之一微米集成电路制造过程中, 如设计线宽小于0.18μm时, 互连导线的延迟有可能大于门电路延迟, 根据RC=2ρε0ε (4L2/P2+L2/T2) , 其中:

ρ为电阻率, ε0为真空介电常数, E为互连导线介电常数, L、P、T分别代表互连导线的长度、宽度和厚度, 可知采用高导电率的互连材料或低介电常数的介质材料是减小互连延迟的途径。1998年9月IBM成功推出400MHz Power PCTM 740/750电路, 再次证明铜互连技术的作用。图4显示了铜互连技术的优越性。但是, 铜基底层沉积, 铜填入及化学机械抛光等关键技术均有待进一步完善, 同时降低这些工艺过程中的铜污染亦成为当前的重要研究课题

图4 在集成电路工艺中采用铜互连技术和铝互连技术的比较

Fig.4 Comparison of the different interconnect materials and processes

Istratov[27]等人重新研究了铜在硅中的扩散及扩散系数与p型掺杂浓度的关系, 指出铜作为带正电荷离子在硅晶格中的扩散不仅与温度, 而且与样品的导电类型和掺杂水平有关, 并得出铜的有效扩散系数的显性表达式为:

\(D_{\text {eff }}(\mathrm{Cu})=\frac{3 \times 10^{-4} \exp (-2090 / \mathrm{T})}{1+2.584 \times 10^{-20} \exp (4900 / \mathrm{T})(\mathrm{Na} / \mathrm{T})}\)

他们发现铜沉淀在本质上是两性的, 当费米能级位置变化时, 铜沉淀可从荷正电变为荷负电[28]。

80年代中期, 掺铒硅在光激发或电子注入条件下, 在1.54μm处观察到了发光现象[29], 这引起了研究者的广泛兴趣。麻省理工学院Kimerling研究组与贝尔实验室合作研制了波长1.54μm的掺铒硅发光二极管, 并继续开展掺稀土杂质硅材料光电子学方面的基础研究[30], 有关半导体材料稀土掺杂的理论及应用, 请参阅文献[31]。

《5 非金属元素的控制及其与缺陷互作用的研究》

5 非金属元素的控制及其与缺陷互作用的研究

氧、碳、氢、氮是硅中研究最多的四种非金属元素。关于氧、碳杂质, 通常的做法是控制硅中氧含量, 降低碳含量。一般的集成电路工艺仍然使用间隙氧含量在 (1~1.4) ×1018 cm-3 (ASTM旧标准) 的硅衬底。此外, 氧沉淀一直是令人瞩目的研究课题, 大量实验表明, 在1000℃以上的集成电路工艺中, 氧沉淀密度与间隙氧浓度有1/6至1/8次方的关系。这意味着要想把氧沉淀密度控制在±10%以内, 则原始间隙氧浓度偏差不能大于±2.5×1016 cm-3。因此, 无论对于单晶控氧还是检测来说都是一个难题。令人可喜的是, 最近二次离子质谱 (SIMS) 的测氧精度有所提高。硅单晶中氧的浓度由固/液交界面处的熔体及整个熔体中氧的分布决定, 并受溶解速度、熔体中的输运状态 (通过对流和扩散) 以及自由熔体表面和熔体与坩埚壁接触面之比的影响。而二氧化硅溶入硅熔体中的量取决于坩埚壁的温度、坩埚旋转速度和熔体中液流的不稳定性等因素。

控制直拉硅中轴向和径向氧的分布的研究方兴未艾。有人在传统的直拉法中采用了磁场[32], 并开发出垂直与水平磁控直拉法 (VMCZ和HM-CZ) , 使用磁场控制直拉单晶中氧含量的实验还在继续, 实验证明, 磁场可有效地用来控制硅单晶中的氧[33], 对改善200 mm以上的大直径单晶的均匀性具有实际意义, 现普遍采用的cusp磁场的磁力线如图5所示。

在集成电路工艺中, 氧对金属杂质的内吸 (IG) 是有益的[34], IG可延长少数载流子的寿命并提高器件成品率。由于电路的设计线宽不断减小, 氧浓度及其轴向和径向均匀性的精确控制, 在硅单晶的生长工艺中显得更为重要。当前200 mm的硅单晶可以达到± (7.5~10) ×1016 cm-3的指标, 径向梯度<5%。对于直径300 mm的硅单晶, 尽管难度很大或成本很高, 但仍可能达到±7.5×1016 cm-3或更低的指标。

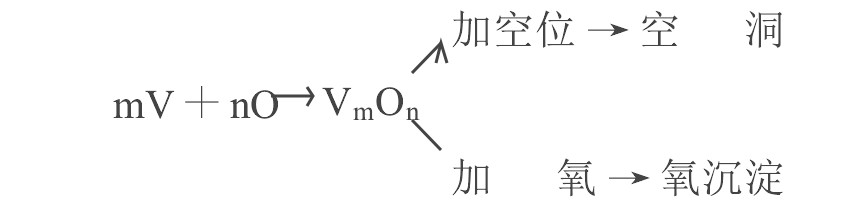

硅晶体中的点缺陷与氧的相互作用对材料质量和集成电路性能有着重要影响。在大直径硅单晶中氧和空位的浓度很高, 间隙氧产生压应力场, 而空位产生张应力场, 异质成核的势垒比均质成核要小得多。Bae等人[35]提出形成缺陷的两条途径如下:

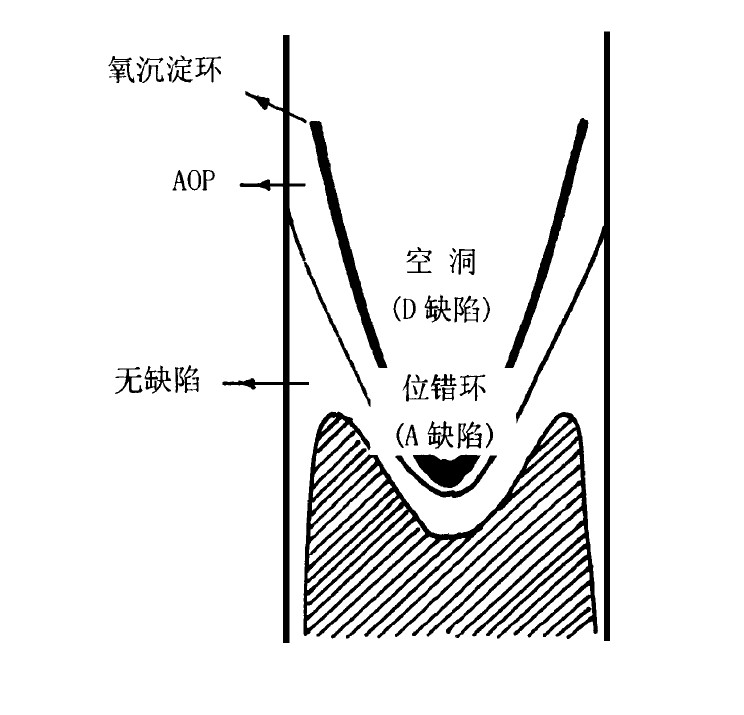

该课题组认为, 单晶冷却时主要的缺陷成核物是补偿晶格应力的空位-氧复合体, 并经历结晶、点缺陷扩散、点缺陷团聚并长大和形成异质氧沉淀等四个过程[36], 图6给出了点缺陷浓度的变化和形成的各类缺陷在晶体中的位置。同时, 他们还发现了反常的氧沉淀 (AOP) 成为氧化层错的核。图7为直拉硅单晶纵剖面上的缺陷分布图。

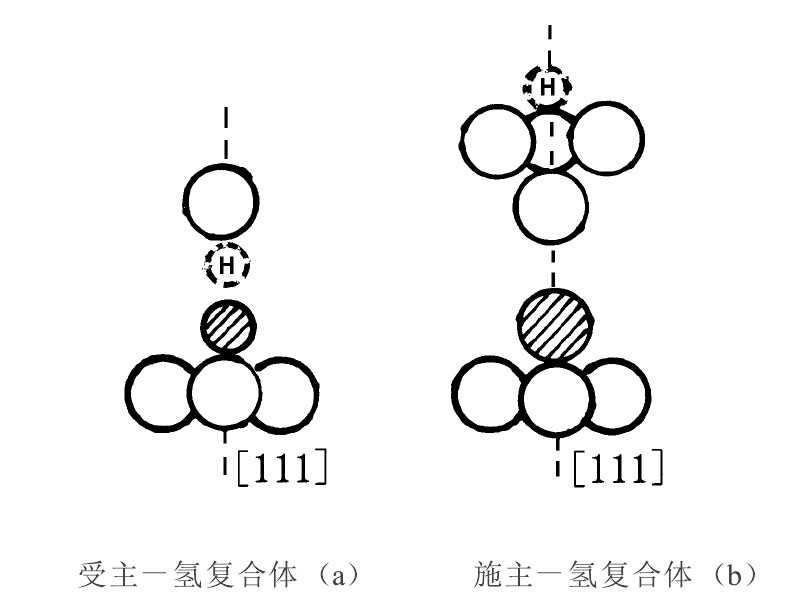

硅中氢的行为, 特别是有关氢对缺陷和杂质的钝化作用的研究已有较长的历史, 但最近由于SMART-CUT的SOI材料的实用化和经氢高温热处理的“高级硅片”的商品化, 使众多的研究工作者更加关注氢注入后硅中缺陷的行为以及相关的动力学特征。王敬、屠海令等人[37]采用高压透射电子显微镜在1MV加速电压和室温至650℃加热条件下, 对氢离子注入硅片中的缺陷进行了原位观察, 建立了硅中氢以分子形式扩散的模型。Stavola[38]评论硅中氢可与许多缺陷作用, 并在与本征点缺陷作用中扮演很重要的角色。氢不但可与施主或受主杂质形成复合体 (图8) , 而且还能在硅中形成分子。Weber等人[39]观察到两种氢分子状态, 其中一种是高度可动性分子, 不仅在晶格间隙中存在, 且极易被空洞俘获, 并具有与氢气相似的拉曼谱特征。

氮在硅中行为也引起了一些研究者的兴趣, 有人以掺氮来提高硅片的机械强度从而减小热处理导致的翘曲, 并发现掺氮硅单晶中存在氮氧复合体及与氮相关的新施主。也有研究者报告, 硅中氮氧复合体可抑制热施主和新施主的形成[40]。

《6 硅基材料研究进展》

6 硅基材料研究进展

《6.1 硅外延材料》

6.1 硅外延材料

双极、CMOS和BiCMOS超大规模集成电路对外延材料的需求有增无减, 外延层变得越来越薄, 参数越来越严格, 并要求有足够的平滑区和陡峭的过渡区。一个好的外延系统中的反应器和基座都是采用近乎无污染的材料制成, 氢气中含氧量小于2×10-9, 含水量控制在 (50~150) ×10-9之间。近年来在外延设备和技术方面已开发出低温外延、光外延、等离子CVD、减压CVD和选择外延等。新的研究结果还表明, 衬底杂质向外延层外扩有弊有利, 如衬底间隙氧向外延层的反扩散可以阻止位错形成和传播, 使器件微结构不受破坏[41]。目前直径200 mm的硅外延片虽然价格偏高, 但在深亚微米集成电路应用中仍具有一定的竞争能力, 这主要是由于外延层可做到微缺陷较少, 均匀性好, 是理想的高密度、高性能逻辑电路的初始材料。目前200 mm硅外延层可做到≥0.125μm的表面颗粒小于50个;表面金属污染量为1010~1011cm-2, 表面微粗糙度可做到0.1 nm。

《6.2 锗硅材料》

6.2 锗硅材料

锗硅 (SiGe) 材料既可与现有的超大规模集成电路硅工艺兼容, 又能够实现“能带工程”, 是未来微电子产业中主要的硅基材料。Paul[42]给出了设想中的集成电路芯片结构, 列举了SiGe的多种用途, 如HBT、光探测器、光波导、量子器件等, 展示了其广阔的发展前景。众所周知, Si与Ge之间有4.2%的晶格失配, 由于SiGe的晶格常数基本上符合Vegard定律, 因此在Si衬底上生长SiGe材料亦存在较大的晶格失配制备可供集成电路使用的SiGe材料一直是硅基材料研究中的前沿课题。SiGe材料生长技术大致有固源分子束外延 (固源MBE) , 气源分子束外延 (GSMBE) 和超高真空化学气相沉淀 (UHVCVD) 三种。一般认为, 固源MBE可独立调节各生长参数, 控制生长过程比较精确, 但目前还不能批量生产SiGe材料。UHVCVD和GSMBE[43]均有易于批量生产的优点, 但系统内流体动力学过程十分复杂。最近, 以UHCVD方法获得了一致性和重复性较好的材料, 使用SiGe材料制备HBT, MODFET共振隧穿二极管 (RTD) 和光电子器件方面也取得了长足的进展[44、45]。

《6.3 SOI材料》

6.3 SOI材料

在未来的“漫游电脑”时代, 需要大量低电压、低功耗高速集成电路, 因此SOI材料可以做为传统硅材料的补充, 发挥更大的作用。近几年, SOI材料完整性不断提高, 已先后于1989年和1991年制做出64k和256k静态随机存储器, 1998年8月, IBM公司宣布在SOI材料上研制出了高性能的微处理器芯片[46]。SOI材料在提高电路集成度、运行速度和抗辐射能力以及减小漏电流方面明显优于体硅和外延材料。其中发展较快的有SIMOX、BESOI和SMARI-CUT三类材料 (图9) 。典型的SOI材料的表面硅薄层厚度为0.1μm~2μm, 埋层二氧化硅厚度为0.2μm (CMOS电路) 至1.0μm (双极型电路) 。BESOI材料中的缺陷密度低, 更接近传统硅片, 但界面缺陷和顶层硅的厚度控制没有完全解决;相比而言, SIMOX材料缺陷密度较高, 埋层二氧化硅内针孔及杂质污染比较严重, 但表面硅层和埋层二氧化硅厚度可精细控制, 与现行集成电路工艺匹配较好。近两年, SMART-CUT材料的研究有较大的进展。其原理是利用H+离子注入, 在硅片中形成气泡层, 经与另一支撑片键合后, 进行高温热处理, 使注氢片从气泡层处裂开, 最后经化学机械抛光后, 得到高质量的SOI材料。现在法国SOITEC公司可批量提供5、6、8英寸的SMART-CUT片。表3给出了1998年SOI材料计划达到的技术指标。目前, 降低成本是SOI材料的主要奋斗目标。

图9 SOI材料制备工艺流程图

(a) —SIMOX; (b) —BESOI; (c) —SMART-CUT

Fig.9 SOI manufacture technologies description

《7 表面形貌与表面质量控制》

7 表面形貌与表面质量控制

众所周知, 集成电路密度每3年提高4倍, 每一代DRAM的光刻线宽的缩小系数为1.46, 相应的硅片平整度也要不断提高。因此, 几年前就有人建议局部平整度的读数应为光刻机景深的1/2或1/3, 而局部平整度SFQR读数大致与光刻线宽相当。目前似乎大部分厂商均能提供0.25μm电路工艺所需的硅片。千兆位级集成电路 (GLSI) 的套刻将超过30次, 因此, 如何使硅片局部平整度适应并满足不断缩小的光刻线宽, 是对硅材料技术工艺的严峻挑战。一般认为, 对应于标称焦深比DOF为0.45μm的光刻设备和工艺, 硅片的局部平整度应为0.1μm。此外, 90年代初又引入了微粗糙度的概念, 系指硅片表面纳米量级的起伏变化, 它将影响GOI和深亚微米集成电路的成品率和性能。大直径硅片的抛光、化学清洗、热处理等工艺都是影响微粗糙度的主要原因。最近, 研究人员已普遍使用原子力显微镜 (AFM) 在线测量硅片表面微粗糙度, 同时还研究了硅片表面微区变化与器件性能间的关系。

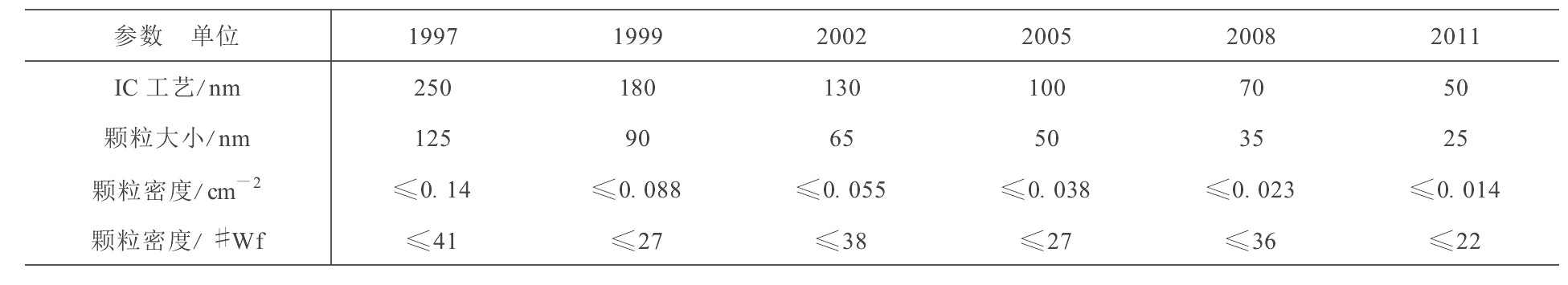

硅片表面颗粒污染仍然是导致器件成品率降低的主要原因, 控制这类污染要同时做好以下两个方面的工作:材料厂家保证原始硅片符合技术指标;在器件制作过程中监控颗粒污染以减少有害缺陷, 这类有害缺陷的大小一般为集成电路线宽的1/3到1/10。表4列出了有关硅衬底材料表面颗粒度的部分参数指标。随着集成电路特征尺寸减小, 气体及化学试剂中残存颗粒的作用也更加明显。已有大量实验数据证明, 范德瓦尔斯力以及静电作用是影响落在硅片表面颗粒密度增高的主要因素, 但由气体、试剂、高纯水以及封装环境气氛产生的颗粒向硅片表面传递的机理仍须进一步研究。从测试角度来看, 表面微缺陷与小于0.2μm的颗粒的检测将互相干扰, 难以区别。如果表面微缺陷不能控制的话, 则局部光散射点 (LLS) 密度会大大超过允许值。LLS是一个简便而实用的概念, 它包括表面粗糙度、雾缺陷 (小的浅坑) , 表面化学残留物、表面颗粒、表面结构缺陷, 有时可能也包括小的外延层错。采用这一指标可避免区分以上各类缺陷, 但是对于未来的纳米级 (特征尺寸<0.1μm) 集成电路来说, LLS及颗粒的大小与密度的指标仍是一个悬而未决的问题。换言之, 在未来的10年内, 对这类污染的检测方法与技术以及降低其密度的研究将是半导体材料研究人员面临的极富挑战性的课题。

《表4》

表4 1998年《国际半导体技术指南》中所列硅片表面颗粒度的最新指标

Table 4 Si wafer surface particle requirements in The International Technology Roadmap for Semiconductors (1998)

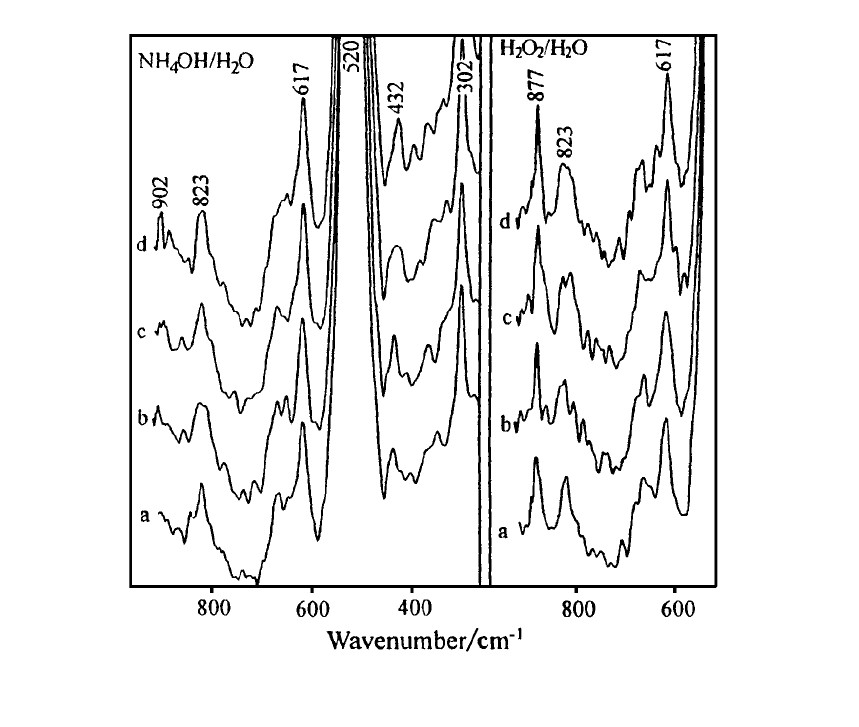

为了提高硅片表面的质量, 在半导体工艺中使用的去离子水, 氧含量为20×10-9。Wang J, Tu H等人[47]使用共焦拉曼光谱技术对硅片表面在各种清洗液中的变化进行了系统的原位观察, 分析了硅材料表面的污染物结构, 研究了硅片在SC-1、SC-2及稀氢氟酸、双氧水、水等溶液中, 其表面硅氢键Si-H3、Si-H2以及Si-H的出现和变化过程 (见图10) 。

由于集成电路对硅片表面质量的要求不断提高, 硅片厂的成本呈指数式增长, 其原因为全部加工过程的设备和材料都要在洁净和高纯环境中进行, 整个自动化系统及硅片传输需要有氮气保护和高真空条件。而高纯度原辅材料, 特别是电子级的化学试剂及气体的使用使加工过程及加工设备成为主要的污染源;污染控制的关键在于使用自动、灵活的集群化设备。因此, 设备供应商和用户必须合作并建立一种新的超净概念。近年来, 无污染制造 (CFM) 的重要性越来越为国际半导体界所认识, 使用超净设备不但可减少硅片的缺陷, 提高集成电路的成品率, 而且还能延长设备使用寿命并提高其可靠性。目前, SEMI标准中关于每片颗粒数的指标没有考虑工艺过程的影响, 当电路集成度非常高时, 工艺过程的影响将上升为重要的因素, 必须严格控制设备环境, 减少颗粒产生。统计数字表明, 设备连续运转污染最小, 而设备搁置则会使颗粒污染增强。硅片的传输过程及容器也是重要的污染源, 因此, 持续使用的片盒需要认真清洗, 才能满足要求在惰性气体中传输则要求气体中氧和水surface immused in NH4OH/H2O and H2O2/H2O分含量均小于10×10-9。此外, 污染控制措施在硅片制备过程中的成本越来越高, SMIF技术已引起了人们的重视, 并开始在材料工艺线上使用。同时, “迷你环境”的应用也大大降低硅片的制造成本。“迷你环境”的概念是将硅片与外界污染隔离开。O′Reilly和Rhine计算了一个新的以100级超净线和0.1级“迷你环境”组成的5000平方英尺的超净间的成本, 比传统超净间造价低52%。在ULPA (超低穿透空气过滤器) 方面降低了54%。

图10 浸泡于NH4OH/H2O和H2O2/H2O溶液的硅片表面原位拉曼谱线变化

a) —0 min;b) —10 min;c) —20 min;d) —30 min

Fig.10 In-situ Raman spectra for Si wafer

与此同时, 对表面质量控制有重要影响的清洗技术研究也有了新的进展。IMEC公司挑战有30年历史的RCA清洗工艺, 报道了一种有效去除表面颗粒和金属的清洗方法[48]。该方法包括两个步骤, 第一步使用H2SO4∶H2O2=4∶1的溶液, 在90℃下生长1.5~2 nm厚的氧化层;第二步使用0.5%HF和0.1%IPA的水溶液, 于室温去除氧化层。此法还大大减少了酸的用量, 有利于环境保护, 其不足之点是在硅片上形成疏水表面而不是亲水表面。现在, 众多的研究人员仍在致力于简化清洗工艺, 减小所用化学试剂的浓度以及有效地控制硅片表面质量的研究[49]。此外, 国际上硅材料产品及相关检测标准平均每2~3年制定、修订一次。由于大直径硅片的缺陷和污染物尺寸和密度急剧减小, 其测量方法和测量技术也将发生变化[50]。可以预计, 进入亚四分之一微米集成电路时代以后, 将大量地引入原位检测、无损测量和实时反馈控制技术以及新的数学统计方法

《8 结束语》

8 结束语

随着跨世纪期间半导体产业高潮的到来, 硅材料将以高质量、低成本为主要目标, 向标准化设备、厂房, 新的加工处理工艺和大直径化方向发展。半导体硅及硅基材料的结构、力学、化学和电学特性的研究会随之不断深入;其缺陷控制、杂质行为、杂质与缺陷互作用及表面质量仍将是工艺技术研究的主攻方向。深亚微米、亚四分之一微米乃至纳米级集成电路用硅及硅基材料是一个新的大系统工程, 要求材料、试剂、气体、设备、检测、器件制造等各方面的研究单位、公司建立伙伴关系, 及时提出问题, 组织合作研究, 共同投资开发, 分享技术成果。未来的研究将包括在原子尺度上合成理想的结构材料, 制备有实际应用前景的硅基光电材料, 开发能降低生产成本的各种新工艺, 使材料满足并适应信息产业软件和硬件发展的需要和变化, 这些将是下个世纪知识经济蓬勃发展的基础和希望所在

京公网安备 11010502051620号

京公网安备 11010502051620号