《1 前言》

1 前言

随着电路设计进入 SOC 时代,产生了将数字电路部分和模拟电路部分集成到同一块芯片上的设计要求。然而在整个电路设计中,模拟电路部分设计是最具挑战性的,并且存在着设计周期长的问题,因而成为 SOC 设计的瓶颈[1] 。在工业界设计中,由于缺乏模拟电路的自动设计工具,常常需要很有经验的专家手工设计和优化系统的模拟部分,才能满足和提高整个商用芯片的性能[2,3] 。

在解决模拟电路自动化设计问题方面,模拟电路自动综合是最好的、最具有发展前景的一种方法。设计者利用模拟电路综合工具,就可以根据特定的应用环境自动、灵活地产生相应的模拟集成电路。模拟集成电路的综合大多是在给定网络结构和电性能指标的条件下确定网络中各元件的最佳参数值,这实质属于参数优化的范畴。它们采用数值最优化技术解决模拟设计中的自由度问题,在给定性能指标情况下,对电路性能进行最优化。在最优化程序中的每次迭代中,要对电路性能进行评估。根据性能评估的方法,可以分为两类:基于仿真和基于性能方程方法[4~6] 。

基于仿真器设计精度很高,但由于完成一次自动综合需要进行数万次、甚至几十万次的迭代,所以,一般因设计时间太长而难以忍受。

基于性能方程的方法利用简化的器件模型和电路模型,推导出一组描述电路性能的方程,在每个迭代点上利用这组性能方程来评估电路的性能,因此完成设计时间远远少于基于仿真器的优化方法,但是其有一个致命的不足,即设计精度差,文献[7]提到:在大多数情况下,考虑一阶效应的电路性能方程与电路仿真器(如 Hspice)仿真结果最大相差 20 %,极端情况下两者之间相差 200 % 。这一缺点将导致最终的设计结果可能是错误的,不可用的。

针对基于性能方程的方法所采用性能方程精度差这一重大缺陷,笔者提出一种改进的基于性能方程法的自动优化方法,其首先通过符号分析法实现模拟单元电路性能的自动建模;接着在遗传优化算法中,采用这组符号模型评估电路性能,从而实现电路性能自动优化。

《2 优化设计方法的思想》

2 优化设计方法的思想

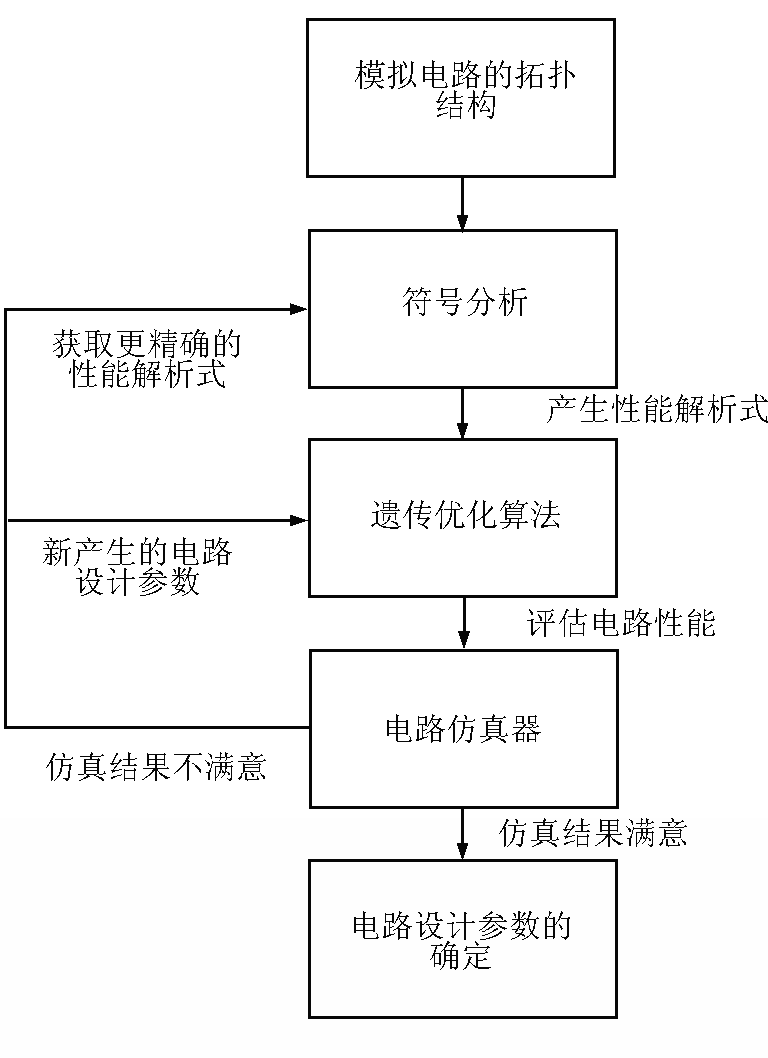

笔者提出的优化思路:首先通过符号分析法得到晶体管的尺寸/无源器件量值等物理参数组成的电路性能符号方程,并对产生的性能方程精度进行验证,进而得到逼近误差最小的性能方程;在此基础上,通过遗传寻优算法对电路设计参数进行优化,即计算、调整、评估;经过多次迭代后,最终把确定的设计参数量值输入到 Hspice 中对电路进行模拟仿真验证,优化方法流程如图 1 所示。

《图1》

图1 自动优化设计方法的流程图

Fig.1 The process of automated optimization

从理论上说,该方法完成优化设计的时间远远小于基于仿真的设计方法。这是因为每次对求解方程式得出的电路性能进行评价,进而选出适配度最好的设计参数集合,再进行迭代,各项工艺库参数可以直接从具体工艺库文件中得到,最终求解出的电路参数放入仿真工具中进行模拟仿真验证。而基于仿真方法的每次评价过程首先通过调用仿真工具(如 Hspice)进行仿真,然后再带入高阶器件模型进行计算,并把仿真结果返回给优化算法,最后进行评价。由于解空间巨大,且基于方程的方法每次对性能方程评估所花的时间远远小于基于仿真的花费时间,因而本方法所花费的时间与基于仿真的相比是忽略不计的。

对电子电路进行符号分析在 20 世纪 60 年代受到强烈的关注,20 世纪 70 年代出现了许多基于计算机的分析技术和程序。从 20 世纪 80 年代后期至今,符号电路分析技术得到较快的发展,其中基于矩阵或行列式的分析方法被证明在产生全符号电路分析中是非常有效的,其主要应用在模拟集成电路分析和建模中[8,9] 。本研究所采用的基于矩阵的符号模型自动建立流程分为下面几个部分(见图 2)。

《图2》

图2 符号分析的建模流程图

Fig.2 The process of symbol analysis modeling

1) 首先读入电路拓扑网表文件,该文件可按 Hspice 等格式书写,这样做保留了与现有数值模拟软件的兼容。

2) 电路扩展,即把电路展开成基本元件,如 MOS 管、二极管这类非线性器件用其相应等效模型表示。如果没有指定模型,则使用通用的默认模型。另一方面,如果选用的小信号模型太复杂,最终模型所含的项就会很多,其中多数项对性能的贡献很小,必将大大增加分析时间和存储量,因此根据需要合理选择小信号模型是十分重要的。随后需做一些简化工作,如将并联元件转成一个等效元件,以确定匹配元件等。

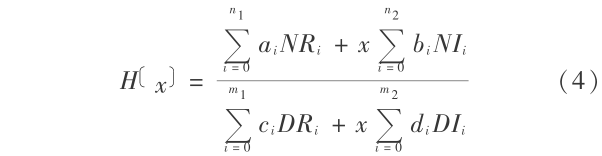

3) 然后便进行各子电路符号方程组的建立和求解工作,实际就是求解符号表达式的工作。其中方程组的建立可采用一般电路分析所使用的方法,如节点法、改进节点法[10] 等,节点法可表述如下:

其中, Yr 是节点导纳矩阵; J, F 为等效电流源、电压源矢量,B,C,D 为电流未知量关系式矩阵; V,I 为要求的节点电压、电流矢量,对符号分析法来说,除未知量 V, I 外,其余各量既可用符号也可以用数值表示。

在求解电路符号方程组时,由于矩阵中含有符号,因此就不能使用常用的数值解法如 LU 分解等来求解方程组,必须采用直接法来解。对矩阵方程 Ax = b,此式中的 A 是系数矩阵,x 是未知向量,常数向量 b 称为右端向量,其解为

其中, Xi 是解矢量的第 i 个分量,D =  , Di 是用 b 代替矩阵 A 中第 i 列后矩阵的行列式。行列式 D 的计算如下,按 D 的第 i 列展开:

, Di 是用 b 代替矩阵 A 中第 i 列后矩阵的行列式。行列式 D 的计算如下,按 D 的第 i 列展开:

其中, Mij 是去掉 D 的第 i 行和第 j 列而得到的行列式,子式  可按上式进行递归运算,这样可节约大量的运算时间和存储量。

可按上式进行递归运算,这样可节约大量的运算时间和存储量。

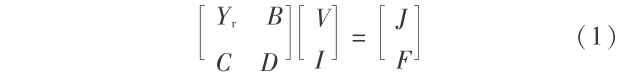

在求得各子电路性能的符号表达式后,为了便于调用,还需将符号表达式整理为如下标准形式:

即将各项按实部和虚部分开,这样不仅分析方便,而且利于进行优化。

4) 随着电路特别集成电路规模的不断扩大,精确的符号表达式通常是冗长和复杂的,对于一个稍复杂的电路,得出符号表达式有上千项、甚至上万项,不利于设计者进行分析,因此需要采取某些措施来降低符号表达式的复杂度。笔者在研究中采用文献[11,12]介绍的近似准则进行简化。

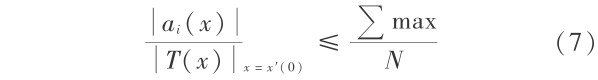

设 T(x)是原符号表达式, T ′(x)是简化后的符号表达式, max 为误差允许的最大范围,则有:

max 为误差允许的最大范围,则有:

其中,x 的范围根据设计要求而定。

由于一个符号表达式往往很复杂,可以认为它是由多项子表达式组成,即:

这样近似起来更为方便,凡是满足式(7)的 ai(x)都将被忽略。

《3 遗传优化算法》

3 遗传优化算法

采用的遗传优化算法具体运行步骤如图 3 所示,它实现的是非基于梯度的搜索,常常被用在复杂系统的优化工作中。此算法模拟了生物演化的过程,从而优化问题中的目标函数。在遗传算法中,每个未知量称为基因,基因的集合组成染色体。采用遗传算法的目的是确定染色体中的基因,使其能最大化适配度函数。在每代中,通过交叉运算和变异运算在评价函数中寻找更好的新染色体个体[13] 。多目标函数的适配度是将遗传算法应用在具体问题中的主要挑战。同时未知量的编码方式也是关系能否应用在具体问题中的另一关键挑战。

《图3》

图3 遗传优化算法的运行流程

Fig.3 Operating flow diagram of the genetic algorithm

《3.1 编码表示》

3.1 编码表示

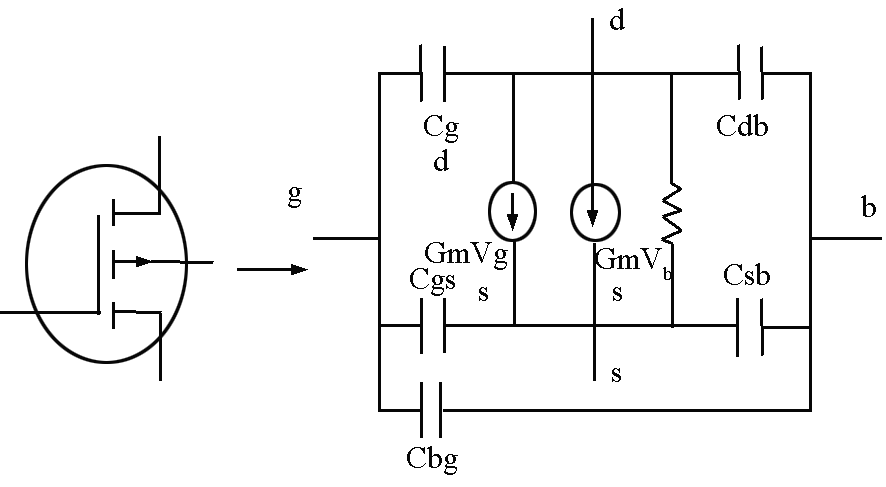

在遗传算法中,每个染色体是一组电路未知物理参数的集合,其隐含表示了电路的一种参数方案。如果需要确定 13 个电路未知物理参数,采用 6 位二进制代码表示每个未知量,因此一个染色体为 78 位二进制代码,从而实现了电路和算法之间的结合。具体染色体格式如图 4 所示。

《图4》

图4 染色体编码格式

Fig.4 The chromosome encoding format

《3.2 适配度函数》

3.2 适配度函数

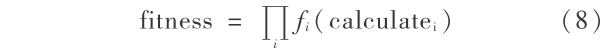

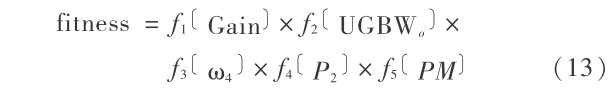

适配度函数是关系到由染色体中基因组计算出来的电路性能好坏的函数(电路性能是否达到期望的数值)。染色体的适配度可以通过下式得到:

其中,calculatei 为由某个染色体中的基因集合计算得出的第 i 种电路性能指标的量值;achievedi 为第 i 种电路性能指标在优化前的量值;fi(calculatei)为某个染色体的第 i 种电路性能指标的适配度;fitness 为某个染色体的整体适配度。

《4 增益增强型运放的自动优化》

4 增益增强型运放的自动优化

具有高增益和大单位增益带宽积的运算放大器(以下简称运放)是高性能 A/D 转换器电路设计中必不可少的。运放的基本性能直接影响到 A/D 转换器的性能。我们所采用的验证电路是应用在 180 MHz,10 位流水线式 ADC 中的增益增强型运放(gain boosted operational amplifier),因此研究具有一定的理论和实际工程意义。

增益增强型运放由 3 个运算放大器组成:一个折叠式共源共栅主运放和两个实现增益增强功能的辅助运放。图 5 为整个运放电路的原理图,图 6 和图 7 分别为以 NMOS 晶体管为输入端的辅助运放 ZAUXN 和以 PMOS 晶体管为输入端的辅助运算放大器 ZAUXP,这两个辅助运放也都是用折叠式共源共栅结构实现,从而得到高的开环增益。

《图5》

图5 增益增强型运放的电路原理图

Fig.5 The schematic of gain-boost op amp

《图6》

图6 辅助运放 ZAUXN 的电路原理图

Fig.6 The auxiliary op amp ZAUXN

《图7》

图7 辅助运放 ZAUXP 的电路原理图

Fig.7 The auxiliary op amp ZAUXP

《4.1 增益增强型运放的符号自动建模》

4.1 增益增强型运放的符号自动建模

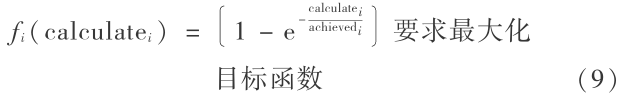

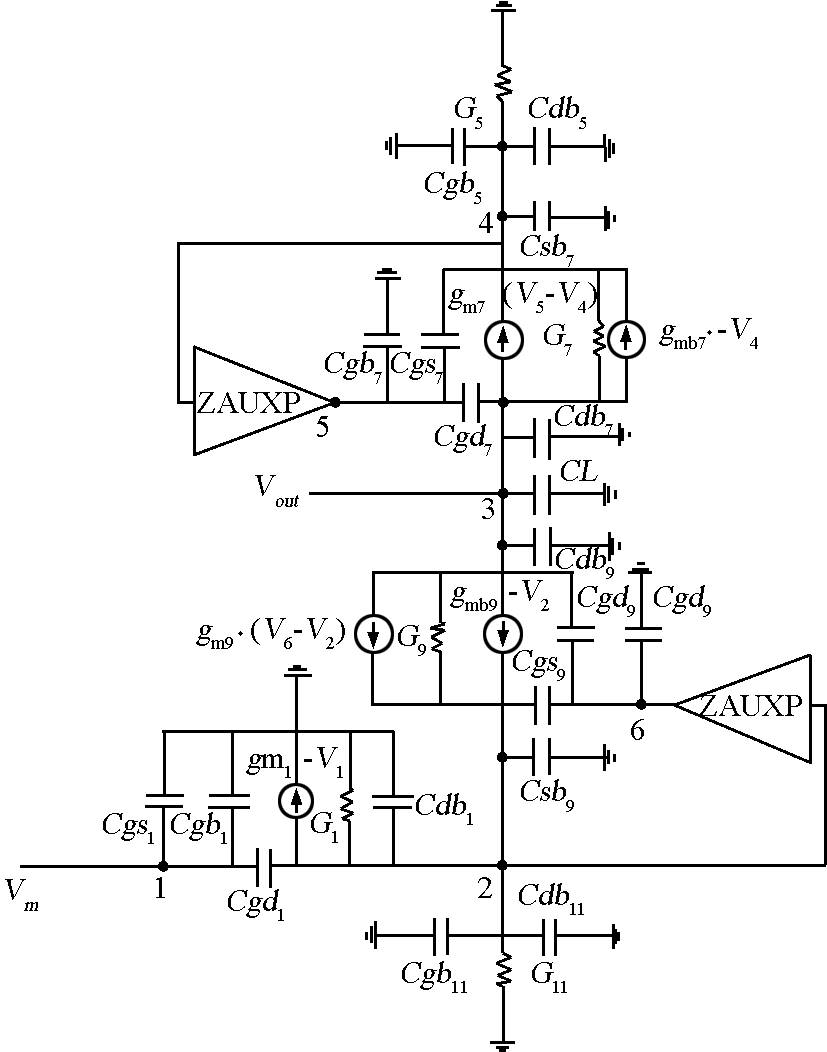

首先,采用完整的 MOS 小信号模型(见图 8)代替电路中的晶体管,同时由于运放的规模较大,为了避免模型的复杂性,首先将辅助运放 ZAUXP 和 ZAUXN 分别等效为一个具有确定增益的双端输入、输出运放,进而根据改进结点法将它们等效为电压控制电压源,从而产生增益增强型运放的小信号等效电路,如图 9 所示。

《图8》

图8 完整的 MOS 小信号模型

Fig.8 The completely small signal model of MOS transistor

《图9》

图9 增益增强型运放的小信号等效电路

Fig.9 The small signal model of gain-boost op amp

在得到运放的等效电路的基础上,采用改进节点法建立起运放的导纳矩阵,然后进行矩阵运算,分别解出输入端(V1)和输出端(V3)的电压,进而可以得出整个运放的网络传输函数,传输函数中的分子和分母是 S 域(频域)的多项式,如果将其完整展开的项数是巨大的,因此这里只给出具有 60 % 精度的传输函数:

A1 · gm1 · A2 · gm9 + S ( A1 · Cgs7 · A2 · gm9 · gm1 ) + S2

( - A1 · Cgs7 · A2 · gm9 · Cgd1 - A1 · Cgs7 · A2 · Cgd9 · gm1

-C4 · A2 · gm9 · Cgd1 - A1 · Cgs7 · gm9 · Cgd1 - C4 · A2 ·

Cgd9 · gm1 - A1 · Cgs7 · A2 · gmb9 · Cgd1 - A1 · Cgs7 · G9 ·

Cgd1 - C4 · gm9 · Cgd1 - C4 · A2 · Cgd9 · gm1 - A1 · Cgs7 ·

gmb9 · Cgd1 - C4 · gmb9 · Cgd1 + gmb7 · A2 · Cgd9 · Cgd1 + G7

· A2 · Cgd9 · Cgd1 + G5 · A2 · Cgd9 · Cgd1 + A1 · gmb7 · A2

· Cgd9 · Cgd1 + gm7 · A2 · Cgd9 · Cgd1 + A1 · gm7 · A2 · Cgd9

· Cgd1 ) + S3 ( A1 · Cgs7 · A2 · Cgd9 · Cgd1 )

G7 · gm7 · G5 · gm9 + A1 · gm7 · G9 · G11 + S ( A1 · A2

· gm7 · C3 · gm9 ) + S2 ( A1 · A2 · Cgs7 · G9 · Cgd9 ) +

S3 · ( A1 · A2 · Cgs7 · C3 · Cgs9 ) ( 11 )

这里, C4 = Cgs7 + Csb7 + Cdb5 + Cgd5 , A1 和 A2 分别为辅助运放 ZAUXP 和 ZAUXN 的放大倍数,值得指出的是:如果要想取得更高精度的模型, A1 和 A2 应该用它们的实际传输函数带入表达式(11)中(辅助运放的传输函数也是根据上述方法求解出来的),而不是简单的直流增益。根据式(11),最终分别得出直流增益 A 、主极点 P1 、次极点 P2 和单位增益带宽 GBW ,另外根据文献[14] 中的公式 PM = 90° - arctan  ,可以得出相位裕度 PM 。

,可以得出相位裕度 PM 。

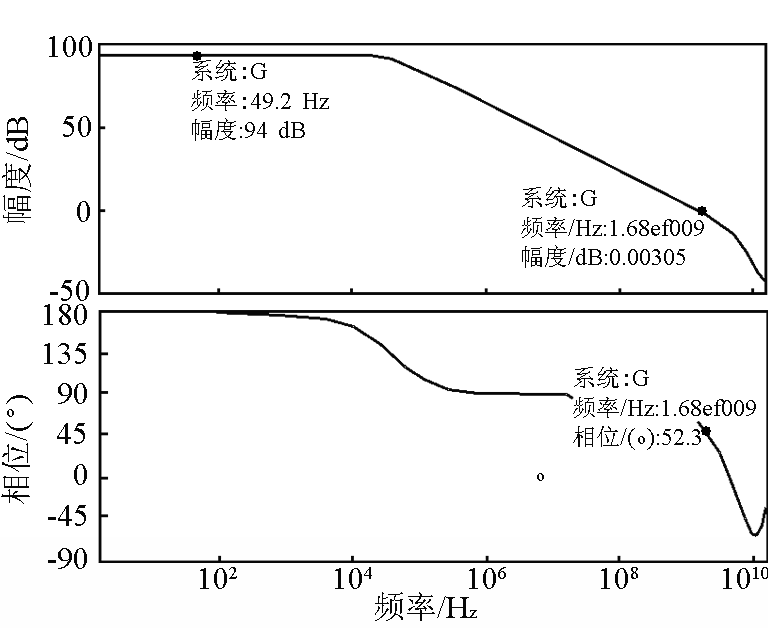

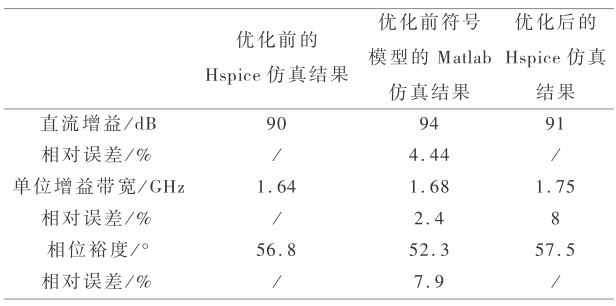

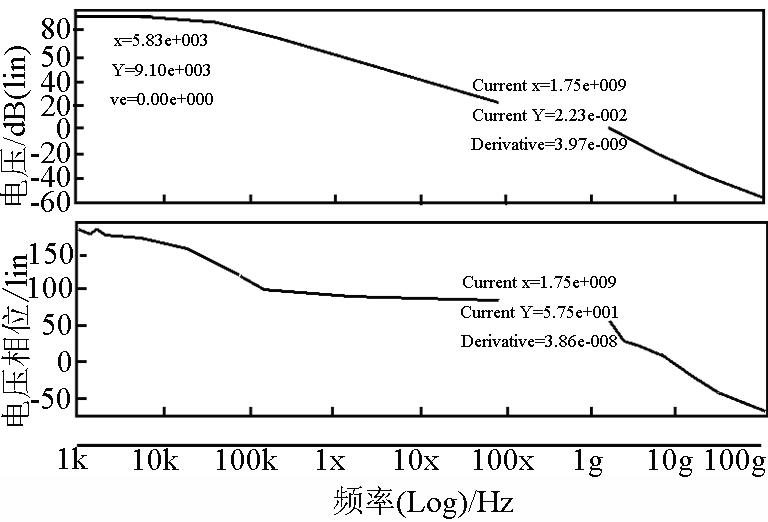

为了验证模型能否担负起自动优化中的评估电路性能的功能,我们进行了 Matlab 仿真结果与 Hspice 仿真结果之间的比较(在 SMIC 的 0.18 μm 工艺条件下进行 Hspice 仿真,符号模型中各物理参数根据工艺文件算出),参见图 10 、图 11 和表 1 。

《图10》

图10 优化前运放 Hspice 的交流分析的仿真曲线图

Fig.10 The Hspice simulated AC analysis results of op amp before optimization

《图11》

图11 优化前运放模型的 Matlab 交流分析曲线图

Fig.11 The Matlab simulated AC analysis results of op amp model before optimization

《表1》

表1 增益增强型运放在优化前后 Hspice 及符号模型的仿真性能指标

Table1 The simulated performances of gain-boost opamp by means of Hspice and Matlab before and after optimization

在图 10,图 11 和表 1 中,可以看出各个电路性能模型基本上满足精度的要求,因此认为这组性能方程能够起到优化中正确评估性能的要求。

《4.2 电路设计经验》

4.2 电路设计经验

在优化增益增强型运放中,引入了电路设计经验以便能更快地取得满意的结果,主要原因是自动优化中的自由度对最终的性能指标影响是非常大的,所以很有必要采用电路设计经验作为自动优化中的限制条件,由于不同电路优化的设计经验不同,因此在程序中留出接口,从而使得程序具有通用性。

根据文献[14,15] ,得出如下的设计经验:

1) 为了保持电路稳定,辅助运放 ZAUXN 的单位增益带宽积 ω4 范围应如下:

其中,  main 为主运放的 3 - dB 带宽; P2 为增益增强型运放的次极点。

main 为主运放的 3 - dB 带宽; P2 为增益增强型运放的次极点。

2) 采用增益增强方法会引入零-极点对,从而导致较缓慢的建立行为;与此同时,由于快速的建立时间要求具备单极点的建立行为和大的单位增益带宽积。因而,在 1)的约束下,尽力提高辅助运放 ZAUXN 的单位增益带宽积。

3) 为了更好地进行频率补偿,增益增强型运放的所有非主极点(包括零—极点对)都应该远远大于运放的单位增益带宽积,从而能取得大的相位裕度。

4) 实现增益增强功能的两个辅助运放中的晶体管应该采用工艺的最小栅长,这样能更好地实现高速的目的。

《4.3 增益增强型运放的优化目标及仿真结果》

4.3 增益增强型运放的优化目标及仿真结果

增益增强型运放是高速、高精度 ADC 中的关键模块,文中所介绍的运放是应用在东南大学 ASIC 中心在研项目 180 MHz,10 位流水线式 ADC 中,为了使运放能满足整个 ADC 系统的性能要求,提出了运放的优化目标,具体如下:

1) 直流增益(Gain) 90 dB;

90 dB;

2) 相位裕度(PM) 53°

53°

3) 单位增益带宽积(GBW) 1.6 GHz;

1.6 GHz;

4) 在设计经验的限制下,尽力提高 ZAUXP 的单位增益带宽积ω4和增强增益型运放的次极点 P2。

根据上述的优化目标,可得染色体的整体适应度,具体形式如下:

首先根据优化前电路的晶体管尺寸来设定优化算法中相关尺寸的范围,从而有效地减少搜索范围,加快收敛速度。进而设定每代有 350 个染色体,经过 120 代进化后,产生和找到适配度最高染色体,经过解码后得到每个电路物理参数的数值,把其输入 Hspice 网表中进行仿真。在采用了中芯国际(SMIC)的 0.18 μm 工艺库和 BSIM3. v. 3 模型、仿真工具为 HSPICE 条件下得出仿真结果,如图 12 所示。

《图12》

图12 优化后运放 Hspice 的交流分析的仿真曲线图

Fig.12 The Hspice simulated AC analysis results of op amp after optimization

所被关注的性能都可以通过 Hspice 中的交流分析直接得到,通过自动优化,可以发现优化后的直流增益、单位增益带宽积、相位裕度的量值均比优化前的量值得到提高,具体数据对比见表 1 。但是应注意到优化后电路的功耗比优化前的有了一定的增大,这符合电路原理。

《5 结语》

5 结语

笔者介绍了一个改进的 CMOS 模拟单元电路自动优化设计方法,仿真结果证明了此方法在实际工程项目应用中的有效性。在此需要指出的是:a. 辅助运放在建模时不能直接等效为电压控制电压源,因为其对相位裕度、极点位置、单位增益带宽有着显著的影响,而对直流增益影响不大;b. 所求出模型目前在自动优化中有着显著优势,但是在自动综合中,目前还不能进行实际应用,因为没有引入偏置电路的建模概念;c. 所采用的建模设计流程,是可以应用于模拟单元电路的自动建模中,前提是设计者给出器件模型的要求;d. 随着计算机计算处理能力不断提高,完全有可能为电路设计者提供一定程度的自动化帮助。

京公网安备 11010502051620号

京公网安备 11010502051620号