《1 引言》

1 引言

驾驶时疲劳、睡眠不足是引发严重交通事故的重要诱因之一。统计表明, 由于疲劳/瞌睡造成的交通事故在交通事故的总数中占7%左右, 在严重交通事故中占40%, 在重型卡车和高速路上的交通事故中, 则占到35%左右。因此许多国家对司机在驾驶中的“瞌睡”检测的研究非常重视。为了适应多媒体通信的发展, 美国德州仪器公司推出了新一代数字媒体处理器TMS320DM642 (以下简称DM642)

《2 DM642简介》

2 DM642简介

DM642是TI最新推出的针对多媒体处理领域应用的 DSP, 它给多媒体设备带来了另一种有效的实现手段。DM642建立在C64系列DSP核基础上, 采用德州仪器公司开发的第二代高性能的先进的超长指令字结构VelociT1.2TM, 其每个乘法器在每个时钟周期内可执行2个16 b乘16 b的乘法或4个8 b乘8 b的乘法。另外6个算术逻辑单元, 在每个时钟周期内都可执行2个16 b或4个8 b的加减、比较、移位等运算。在600 MHz的时钟频率下, DM642每秒可以进行24亿次16 b的乘累加或48亿次8 b的乘累加。这样强大的运算能力, 使得DM642可以进行实时的多视频处理和图像处理。同时在C64核的基础上, 增加了很多的外围设备和接口。主要的结构特征为

《3 疲劳检测系统的构成》

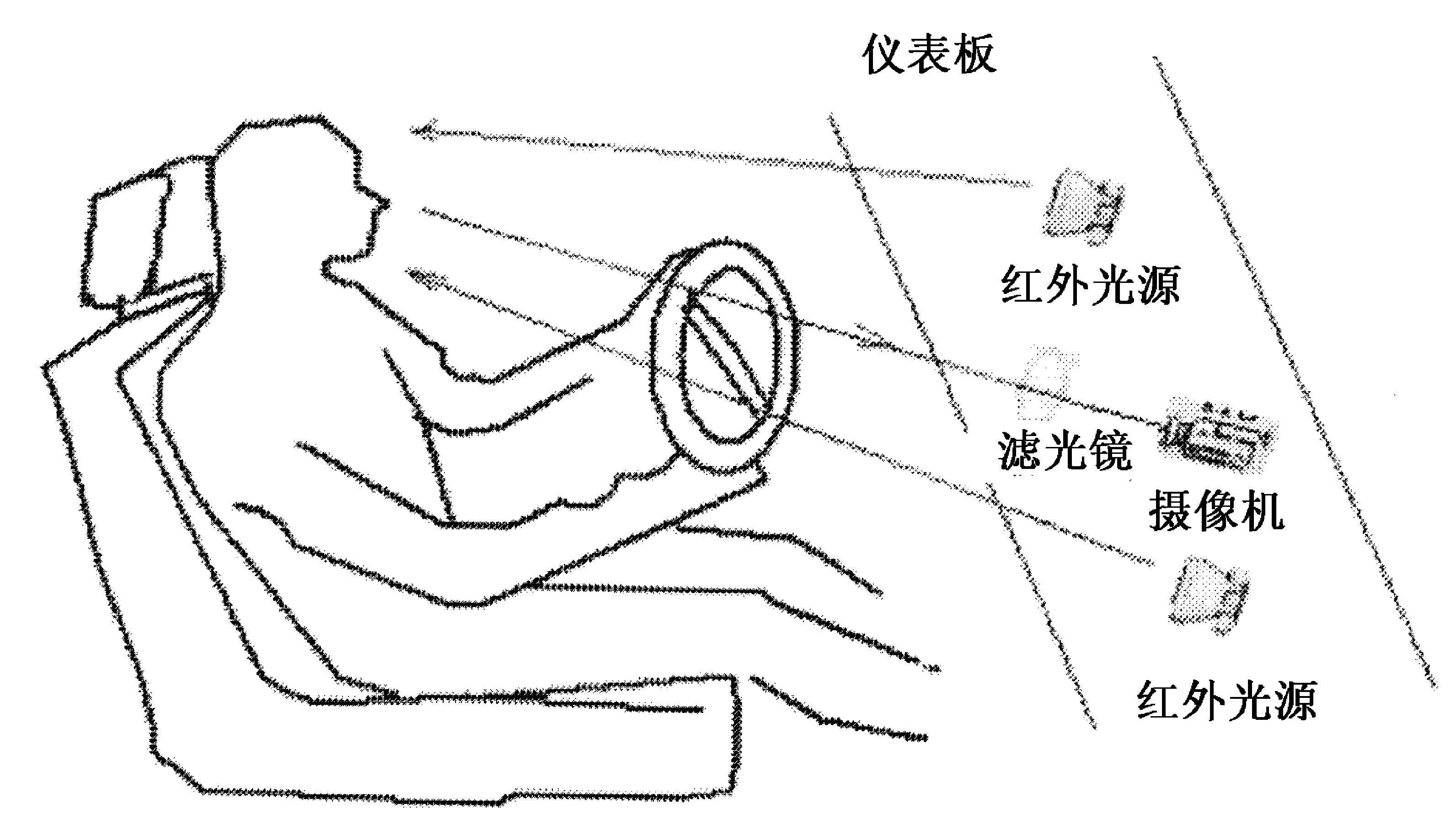

3 疲劳检测系统的构成

疲劳检测系统 (DFS) 旨在检测驾驶员是否疲劳, 以避免因疲劳造成的交通事故。根据疲劳检测算法中要精确定位人的眼睛的要求, 系统结构如图1所示。

DFS主要包括:

1) 红外线敏感的黑白CCD摄像机, 在波长800~900 nm处有较高的灵敏度。

2) 红外线带通滤波器, 中心波长为850 nm, 半带宽12 nm, 峰值通透率为83%。

3) 红外光源。发光二极管的中心波长为850 nm, 功率为10 mW。

DFS具有3个特征:

1) 红外光源与摄像机成一定的角度, 以消除由于光源与摄像机距离过近造成“红眼”现象, 影响测量效果。

2) 利用固定波长的红外光才能通过的红外带通滤光片滤除可见光影响, 使白天与晚上的成像效果相差不大。

3) 使用黑白的红外摄像机, 在波长800~900 nm处成像效果最好, 红外光线对人的视觉没有干扰。

获取较好的头部图像是后续处理的保证, 以上方案会获取亮瞳孔效果, 这对眼睛的精确定位有极大的帮助。在有了较好的图像效果之后就可以对图像进行采集和处理。

《4 疲劳检测系统的电路》

4 疲劳检测系统的电路

《4.1总体框图》

4.1总体框图

疲劳检测实时采集处理系统由图像采集、图像处理和图像输出模块构成。基本工作原理是:CCD采集经过红外滤波的连续的模拟信号, 经过图像采集模块的A/D转换, 变成数字图像信号, 然后再由图像处理模块完成对数字图像信号的运算处理。主要包括图像的预处理、图像分割、特征提出、识别等算法的实现和通过输出模块显示的期望结果以及报警等。系统结构框图如图2所示。

图像采集图像处理

图2 系统模块示意图

Fig. 2 System module

实时图像处理系统设计的难点是如何在有限的时间内完成对大量的图像数据的处理。从人的视觉理论分析, 只有图像处理系统的处理速度达每秒25帧以上才能达到实时的效果, 即要求实时图像处理系统必须在40 ms内完成对一帧图像的运算处理, 才能保证图像的实时性。DM642强大的功能可以很好地满足图像处理的要求。

《4.2图像采集模块设计》

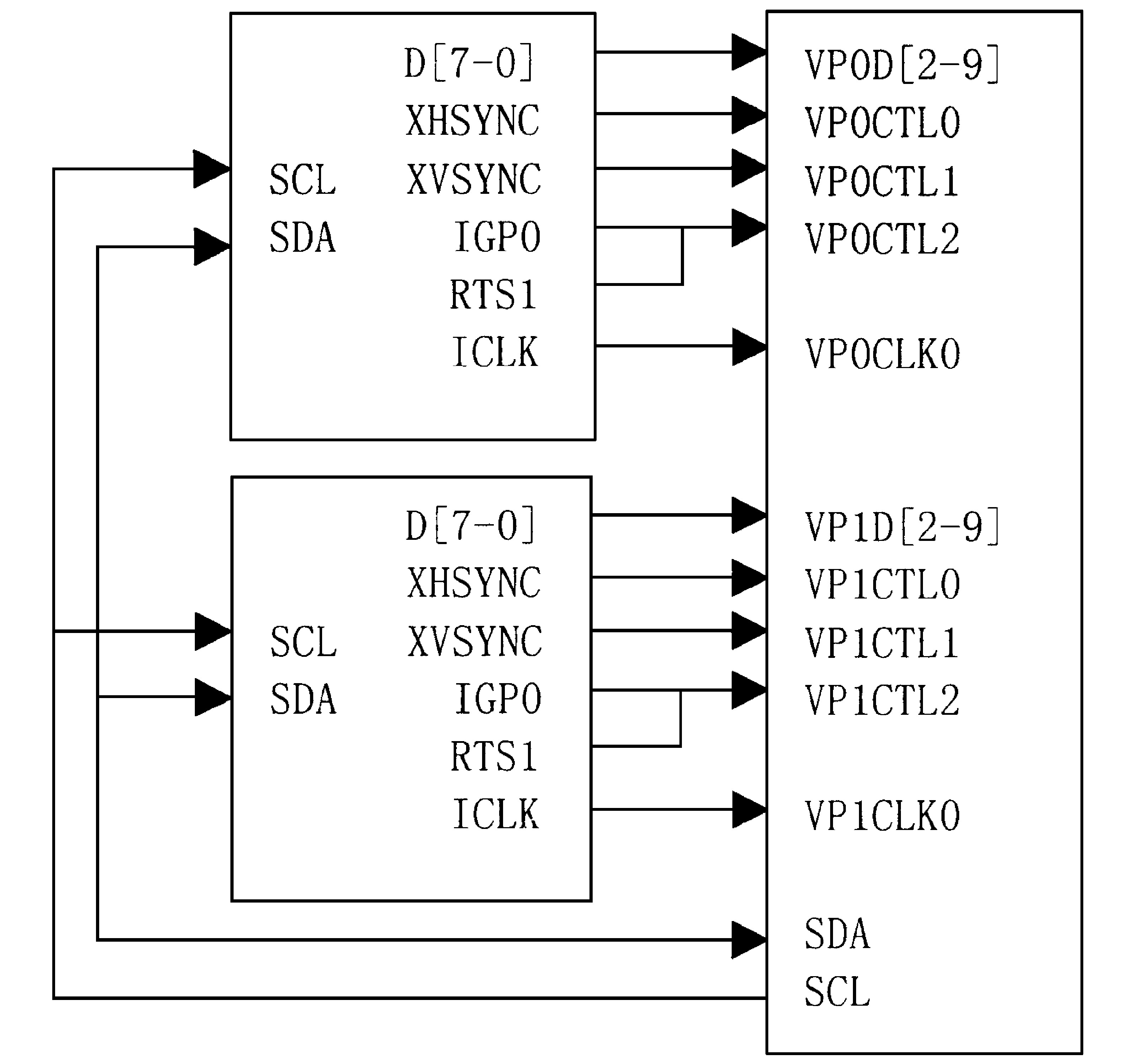

4.2图像采集模块设计

在系统设计中, 使用的图像采集设备是CCD摄像头。由于CCD摄像头输出的是模拟信号, 不能被DSP直接处理, 因此选用了飞利浦的半导体SAA7115图像解码芯片来完成图像的数字化过程, 以及对水平和垂直同步等信号的分离。SAA7115是唯一可提供双9位低噪声、2倍以上抽样模拟到数字转换的视频解码器。SAA7115在信噪比上有重大改进, 为10~15 dB, 是同类产品中视频解码性能最高的。

DM642使用所有的三个视频端口。为了扩展功能, 笔者将视频端口0和视频端口1用作输入端口

SAA7115芯片的输入晶振为24.576 MHz, 其实际工作频率为13.5 MHz。在PAL制式下, 芯片1行最多能采集720点 (不包括行消隐信号) , 1帧最多采集625行 (包括场消隐信号) 。芯片SAA7115有很多种功能供用户选择, 它可以通过对寄存器的设置来完成。由于系统的研究对象是基于256级的灰度图像, 其输入信号采用PAL体制, 结合系统处理速度的具体要求, 系统对芯片作如下配置: a. 格式采用4∶2∶2 YUV信号机制, 只取Y (亮度) 信号;b. 分辨率为512×256像素或者256×256像素。

采集模块的电路图如图3所示

《4.3图像处理模块设计 [1]》

4.3图像处理模块设计 [1]

DM642的结构特征在设计上有很大的自由空间。在图像处理模块中, 扩展了数存、程存。EMIF (外部寄存器端口) 有4个独立的可设定地址的区域, 称为芯片使能空间 (CE0-CE3)

《4.3.1 SDRAM寄存器端口》

4.3.1 SDRAM寄存器端口

在CE0空间连接了64 b的SDRAM总线。选取2片MT48LC4M32B2。该32MB的SDRAM空间用来存储程序、数据和图像处理中间结果等信息。总线由外部PLL驱动设备控制, 在133 MHz的最佳状态运行。SDRAM的刷新由DM642自动控制。

《4.3.2 Flash寄存器接口》

4.3.2 Flash寄存器接口

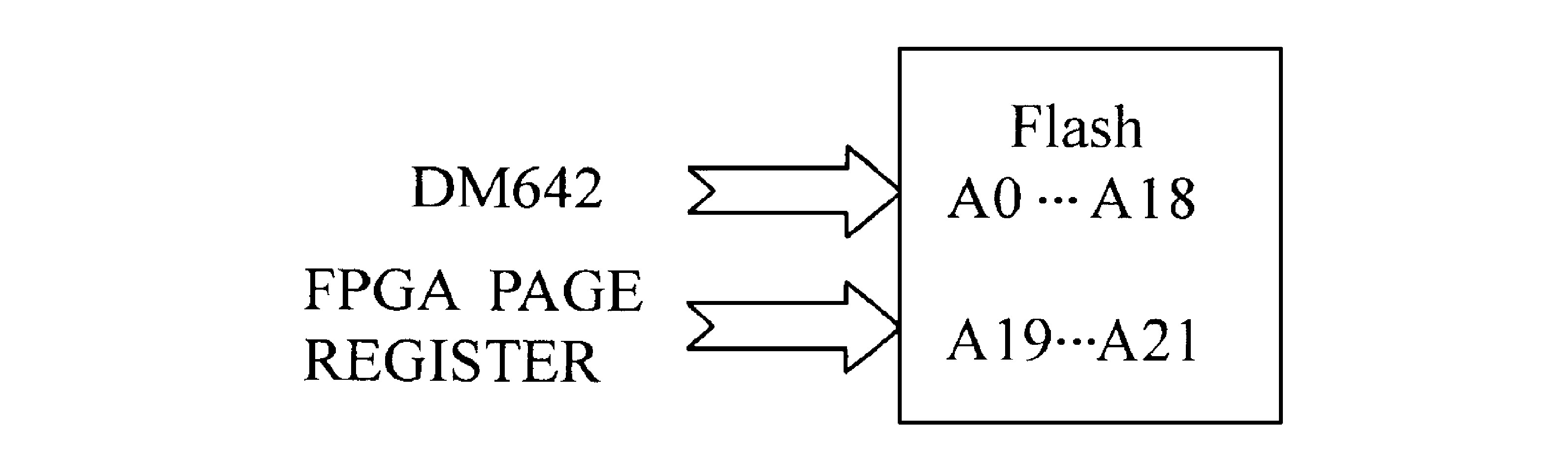

系统扩展4MB的Flash, 映射在CE1空间的低位, 如图4所示。选取4MB×8的AM29LV033C。Flash寄存器主要用来导入装载和存储FPGA的配置信息。CE1空间被配置成8 b, Flash寄存器也是8 b。由于CE1的可利用地址空间小于Flash的空间, 所以利用FPGA来产生3个扩展页。这些扩展的线形地址通过FPGA的Flash的基础寄存器进行定义地址, 复位后默认是000。

《4.3.3 FPGA异步寄存器端口 [4]》

4.3.3 FPGA异步寄存器端口 [4]

系统通过使用Xilinx XC2S300E系列FPGA来实现增强视频功能和其他的一些连带功能。在默认模式下, FPGA通过DM642的视频端口2输出视频到SAA7105。视频编码器FPGA有10个异步存储寄存器定位在CE1空间高位。这些寄存器是:OSD控制寄存器;DMA Threshold LSB寄存器;DMA Threshold MSB寄存器;中断状态寄存器;中断使能寄存器;GPIO方位寄存器;GPIO状态寄存器;LED寄存器;Flash Page寄存器;FPGA Version寄存器。

《4.3.4 FPGA同步寄存器端口》

4.3.4 FPGA同步寄存器端口

FPGA在CE3地址空间开设同步寄存器。这些寄存器主要实现OSD功能和一些连接。

以上工作解决了视频处理中需要大量数据存储空间和程序存储空间的问题。假如要求图像分辨率为640乘480, 每个采样点的灰度层为8位, 则1帧单色图像所占的存储空间为 1 MB, 如果处理算法涉及到n帧图像, 存储空间就为n倍。在疲劳检测算法中需要存储前后2帧图像, 32 MB的数存即足够使用, 而且可以做一些算法上的扩展。图像处理模块框图如图5所示。

《4.4图像显示模块设计》

4.4图像显示模块设计

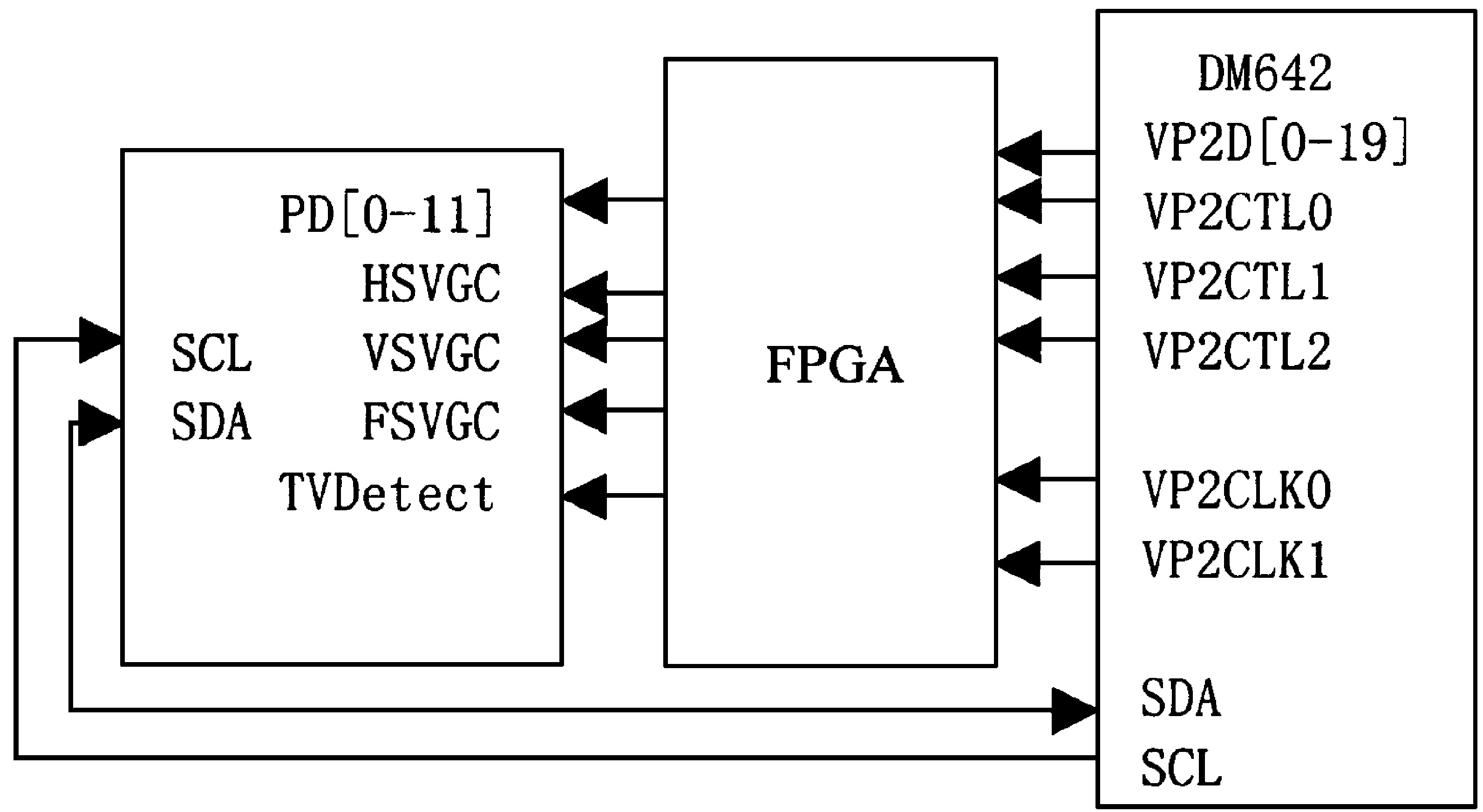

图6为图像显示模块框图。DM642的视频端口2用来驱动视频编码器。它通过FPGA发送, 以实现高级功能, 例如OSD。但它在默认方式下是直接通过视频连接到SAA7105视频编码器。这个编码器可以进行RGB, HD合成视频, 及NTSC/PAL复合视频编码, 也可以对依靠SAA7105内部寄存器编程的S-Video进行编码。SAA7105的内部编程寄存器通过DM642的I2C总线进行配置。

HDTV, FPGA提供增强的时钟;对于OSD, FPGA提供了FIFOs, 将视频端口2的数据与FIFOs端口的数据进行混合。FPGA的FIFOs在CE3空间的同步模式下, 通过DM642的EMIF进行存取。

《5 结语》

5 结语

实现疲劳检测, 对于交通部门和驾驶员都是非常需要的。笔者设计的基于TMS320DM642的疲劳检测系统能够初步实现疲劳检测。该系统在硬件性能方面有很大提高, 并且结构紧凑、调节灵活、可靠性高、实时性强, 为视频处理算法的实现提供了一个平台。

京公网安备 11010502051620号

京公网安备 11010502051620号