1 引言

微控制器 (MCU, micro control unit) 是嵌入式系统的核心, 广泛应用于各个领域。8位MCU IP核具有很高的通用性和灵活性, 可以嵌入到不同的集成电路中, 大大简化设计难度, 缩短设计周期, 降低设计成本。笔者设计的8位MCU IP核采用哈佛结构, 内部单元可简化为时序控制和数据通道两部分, 与Microchip公司PIC16C57完全兼容

2 控制部分设计

《2.1 时序设计》

2.1 时序设计

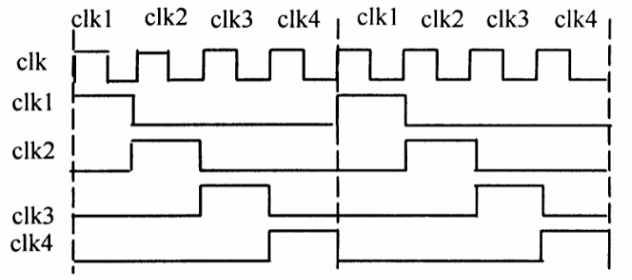

笔者设计的MCU IP核系统时钟clk采用20 MHz, 由时钟分频模块产生四相不重叠工作时钟, 分别为clk1, clk2, clk3, clk4, 如图1所示。每条指令的执行过程都可以看作是固定微操作的依次组合, 笔者在设计过程中把这些基本的微操作依次分配到以工作时钟划分的时间轴中去, 形成MCU的整体时序, 如图2所示。

《图1 四相不重叠工作时钟》

图1 四相不重叠工作时钟

Fig.1 4_Phase non_overlapping clocks

《图2 整体时序设计》

图2 整体时序设计

Fig.2 Design of total timing

《2.2 译码控制单元设计》

2.2 译码控制单元设计

指令译码单元从指令寄存器 (IR) 中读取指令, 完成对当前执行指令的辨认, 通过分析产生一系列的控制信号。该部分主要包括寄存器模块设计和译码模块设计。

指令寄存器 (IR) 采用两级结构、两个12位的寄存器进行设计, 以满足系统两级流水线结构的要求, 其结构如图3所示。其中romdata[11∶0]数据取自程序存贮器, 经两级寄存后, 输出指令数据inst[11∶0]到译码模块。

《图3 指令寄存器结构》

图3 指令寄存器结构

Fig.3 Structure of IR

指令译码模块在实现上通常有两种方式:随机逻辑译码和结构化译码。笔者设计的该款MCU, 由于采用RISC指令集, 共33条指令, 指令少且规则, 故采用随机逻辑译码, 又称为硬布线译码

《图4 特殊指令的译码》

图4 特殊指令的译码

Fig.4 Decoder of special instraction

3 数据通道部分设计

《3.1 数据通道结构》

3.1 数据通道结构

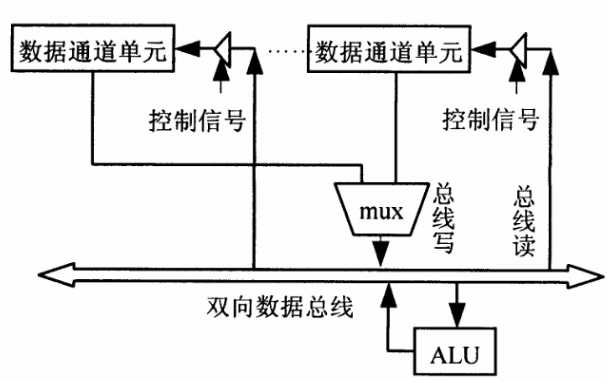

该款MCU IP核的数据通道部分主要包括数据寄存器、专用寄存器、ALU运算单元等几个数据通道单元。笔者在设计过程中, 使用特定的数据通道模型, 通过一条双向数据总线, 对各数据通道单元进行读写设计。其结构如图5所示。此模型可以是多层的, 每个通道组元还可再分为多个子通道组元。模型中双向数据总线充当每个单元源总线及目的总线双重功能, 分别由特定的三态门和多路选择器两种电路结构实现读写操作。

《图5 数据通道结构》

图5 数据通道结构

Fig.5 Sstructure of data path

《3.2 设计实现》

3.2 设计实现

以特殊的数据通道单元ALU为例介绍数据通道部分的设计。ALU是MCU的运算单元, 包括加、减、与、或、异或、非、左移、右移、半字节交换9种运算。笔者设计的ALU采用低功耗设计。通过复用加、减运算单元, 将ALU模块分为8个运算单元, 构成8个子数据通道。在每条指令的执行周期, 由控制信号aluop[3∶0]负责子通道选择, 8个子数据通道始终只有一条处于选通工作状态, 大大降低芯片的动态功耗

表1 ALU不同设计方案功耗分析对比

Table 1 Power contrast for different ALU designs

设计方案 |

cell内部功 耗/μW (%) |

net开关功 耗/μW (%) |

动态功耗 /μW |

低功耗 |

48.877 2 (52) | 41.913 2 (48) | 87.790 5 |

一般 |

232.344 5 (73) | 87.593 5 (27) | 319.938 0 |

4 结论

所设计的MCU IP核工作时序清晰, 体现了自顶向下 (top-down) 的设计方法。控制译码单元采用硬布线译码, 特殊指令特殊处理, 简化了设计;数据通道部分使用特定层次化数据通道模型设计, 结构规整, 设计规范。在设计过程中, 笔者使用Synopsys公司VCS和 DC对该款MCU IP核分别进行仿真和综合, 并进行了功耗分析。综合分析结果得出, 该款MCU IP核总体功耗约在49.598 0 mW, 实现了低功耗设计, 适用于集成到大规模系统中。

参考文献

[1] pic16c5x.pdf[EB/OL].Microchip Technology Inc, 1998

[2] 钟旭恒, 高明伦.基于数据通道指令流程图的硬布线控制电路设计[J].微电子学与计算机, 2001, (5) :8~11

[3] 罗文, 杨波.寄存器传输级低功耗设计方法[J].小型微型机算机系统, 2004, (7) :1207~1211

京公网安备 11010502051620号

京公网安备 11010502051620号